Top-down digital design flow - Microelectronic Systems Laboratory

Top-down digital design flow - Microelectronic Systems Laboratory

Top-down digital design flow - Microelectronic Systems Laboratory

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

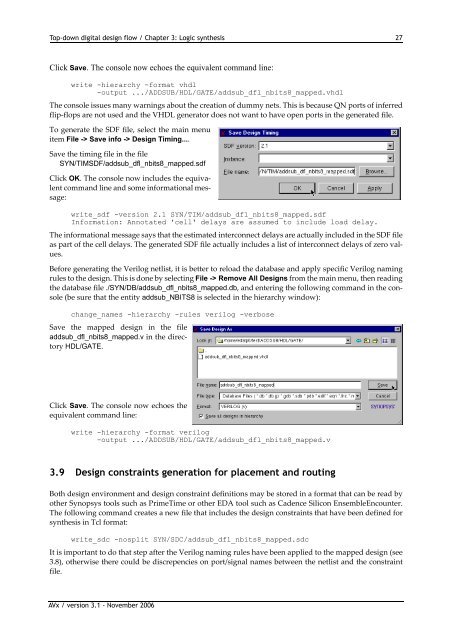

<strong>Top</strong>-<strong>down</strong> <strong>digital</strong> <strong>design</strong> <strong>flow</strong> / Chapter 3: Logic synthesis 27Click Save. The console now echoes the equivalent command line:write -hierarchy -format vhdl-output .../ADDSUB/HDL/GATE/addsub_dfl_nbits8_mapped.vhdlThe console issues many warnings about the creation of dummy nets. This is because QN ports of inferredflip‐flops are not used and the VHDL generator does not want to have open ports in the generated file.To generate the SDF file, select the main menuitem File -> Save info -> Design Timing....Save the timing file in the fileSYN/TIMSDF/addsub_dfl_nbits8_mapped.sdfClick OK. The console now includes the equivalentcommand line and some informational message:write_sdf -version 2.1 SYN/TIM/addsub_dfl_nbits8_mapped.sdfInformation: Annotated 'cell' delays are assumed to include load delay.The informational message says that the estimated interconnect delays are actually included in the SDF fileas part of the cell delays. The generated SDF file actually includes a list of interconnect delays of zero values.Before generating the Verilog netlist, it is better to reload the database and apply specific Verilog namingrules to the <strong>design</strong>. This is done by selecting File -> Remove All Designs from the main menu, then readingthe database file ./SYN/DB/addsub_dfl_nbits8_mapped.db, and entering the following command in the console(be sure that the entity addsub_NBITS8 is selected in the hierarchy window):change_names -hierarchy -rules verilog -verboseSave the mapped <strong>design</strong> in the fileaddsub_dfl_nbits8_mapped.v in the directoryHDL/GATE.Click Save. The console now echoes theequivalent command line:write -hierarchy -format verilog-output .../ADDSUB/HDL/GATE/addsub_dfl_nbits8_mapped.v3.9 Design constraints generation for placement and routingBoth <strong>design</strong> environment and <strong>design</strong> constraint definitions may be stored in a format that can be read byother Synopsys tools such as PrimeTime or other EDA tool such as Cadence Silicon EnsembleEncounter.The following command creates a new file that includes the <strong>design</strong> constraints that have been defined forsynthesis in Tcl format:write_sdc -nosplit SYN/SDC/addsub_dfl_nbits8_mapped.sdcIt is important to do that step after the Verilog naming rules have been applied to the mapped <strong>design</strong> (see3.8), otherwise there could be discrepencies on port/signal names between the netlist and the constraintfile.AVx / version 3.1 - November 2006