Top-down digital design flow - Microelectronic Systems Laboratory

Top-down digital design flow - Microelectronic Systems Laboratory

Top-down digital design flow - Microelectronic Systems Laboratory

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

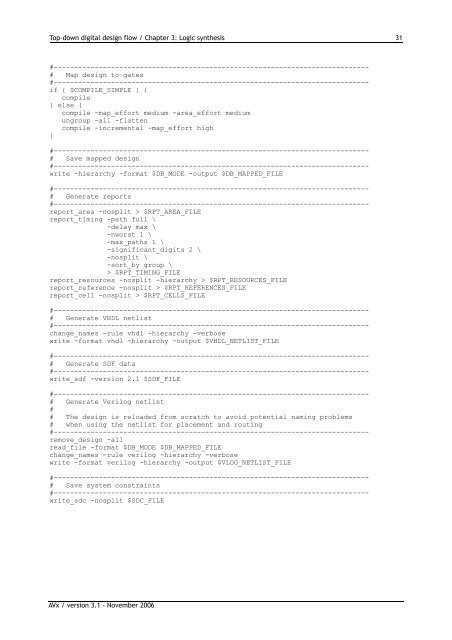

<strong>Top</strong>-<strong>down</strong> <strong>digital</strong> <strong>design</strong> <strong>flow</strong> / Chapter 3: Logic synthesis 31#-----------------------------------------------------------------------------# Map <strong>design</strong> to gates#-----------------------------------------------------------------------------if { $COMPILE_SIMPLE } {compile} else {compile -map_effort medium -area_effort mediumungroup -all -flattencompile -incremental -map_effort high}#-----------------------------------------------------------------------------# Save mapped <strong>design</strong>#-----------------------------------------------------------------------------write -hierarchy -format $DB_MODE -output $DB_MAPPED_FILE#-----------------------------------------------------------------------------# Generate reports#-----------------------------------------------------------------------------report_area -nosplit > $RPT_AREA_FILEreport_timing -path full \-delay max \-nworst 1 \-max_paths 1 \-significant_digits 2 \-nosplit \-sort_by group \> $RPT_TIMING_FILEreport_resources -nosplit -hierarchy > $RPT_RESOURCES_FILEreport_reference -nosplit > $RPT_REFERENCES_FILEreport_cell -nosplit > $RPT_CELLS_FILE#-----------------------------------------------------------------------------# Generate VHDL netlist#-----------------------------------------------------------------------------change_names -rule vhdl -hierarchy -verbosewrite -format vhdl -hierarchy -output $VHDL_NETLIST_FILE#-----------------------------------------------------------------------------# Generate SDF data#-----------------------------------------------------------------------------write_sdf -version 2.1 $SDF_FILE#-----------------------------------------------------------------------------# Generate Verilog netlist## The <strong>design</strong> is reloaded from scratch to avoid potential naming problems# when using the netlist for placement and routing#-----------------------------------------------------------------------------remove_<strong>design</strong> -allread_file -format $DB_MODE $DB_MAPPED_FILEchange_names -rule verilog -hierarchy -verbosewrite -format verilog -hierarchy -output $VLOG_NETLIST_FILE#-----------------------------------------------------------------------------# Save system constraints#-----------------------------------------------------------------------------write_sdc -nosplit $SDC_FILEAVx / version 3.1 - November 2006