Integrator/CP User Guide - ARM Information Center

Integrator/CP User Guide - ARM Information Center

Integrator/CP User Guide - ARM Information Center

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

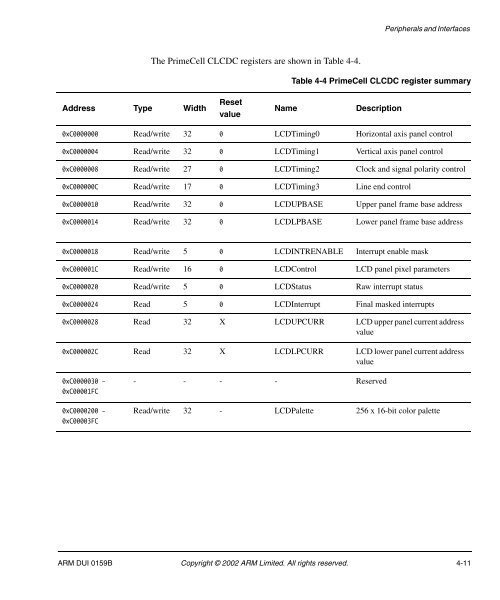

Peripherals and InterfacesThe PrimeCell CLCDC registers are shown in Table 4-4.Table 4-4 PrimeCell CLCDC register summaryAddress Type WidthResetvalueNameDescription0xC0000000 Read/write 32 0 LCDTiming0 Horizontal axis panel control0xC0000004 Read/write 32 0 LCDTiming1 Vertical axis panel control0xC0000008 Read/write 27 0 LCDTiming2 Clock and signal polarity control0xC000000C Read/write 17 0 LCDTiming3 Line end control0xC0000010 Read/write 32 0 LCDUPBASE Upper panel frame base address0xC0000014 Read/write 32 0 LCDLPBASE Lower panel frame base address0xC0000018 Read/write 5 0 LCDINTRENABLE Interrupt enable mask0xC000001C Read/write 16 0 LCDControl LCD panel pixel parameters0xC0000020 Read/write 5 0 LCDStatus Raw interrupt status0xC0000024 Read 5 0 LCDInterrupt Final masked interrupts0xC0000028 Read 32 X LCDUPCURR LCD upper panel current addressvalue0xC000002C Read 32 X LCDLPCURR LCD lower panel current addressvalue0xC0000030 –0xC00001FC0xC0000200 -0xC00003FC- - - - ReservedRead/write 32 - LCDPalette 256 x 16-bit color palette<strong>ARM</strong> DUI 0159B Copyright © 2002 <strong>ARM</strong> Limited. All rights reserved. 4-11