- Page 1 and 2:

SERIES9600 SERVICE MANUAL ERROR CO

- Page 3:

START-UP AND SOFTWARE BOOT Loading

- Page 6 and 7:

SRAM Card Error Codes If an error o

- Page 9 and 10:

Event Codes & Messages The software

- Page 12 and 13:

Event Codes & Messages (Cont.) CODE

- Page 15 and 16:

Event Codes & Messages (Cont.) CODE

- Page 17:

Event Codes & Messages (Cont.) 57 W

- Page 20 and 21:

Low Battery Charge Messages Under m

- Page 23:

Error Messages During Operation (Co

- Page 26 and 27:

Status Menu Chart Use the following

- Page 28 and 29:

PIO Status Use this menu to read th

- Page 30:

Speaker Pitch This menu allows the

- Page 34 and 35:

386 AMI BIOS Post Code Table These

- Page 36 and 37:

386 AMI BIOS Post Code Table (Cont.

- Page 38:

386 AMI BIOS Post Code Table (Cont.

- Page 42:

Nobrk.com Error Codes (Executed by

- Page 45:

Loadip.Exe (Executed By Autoexec.Ba

- Page 49:

Critical Errors Code Description Po

- Page 53:

ii 9600 System Service Manual © De

- Page 57 and 58:

INTRODUCTION PURPOSE This manual co

- Page 59 and 60:

Introduction 3 SAFETY PRECAUTIONS T

- Page 61 and 62:

Introduction 5 EXPLOSION HAZARDS WA

- Page 63 and 64:

Introduction 7 WARNING SYMBOLS The

- Page 66 and 67:

Introduction 9 UNAUTHORIZED MODIFIC

- Page 69 and 70:

SYSTEM OVERVIEW OVERVIEW This secti

- Page 71:

System Overview 3 • Digital image

- Page 74 and 75:

System Overview 5 • Auto and manu

- Page 76:

System Overview 7 Video Monitors

- Page 79 and 80:

System Overview 9 System Configurat

- Page 81 and 82:

System Overview 11 NEUROVASCULAR MO

- Page 84 and 85:

System Overview 13 SYSTEM OPERATION

- Page 86 and 87:

System Overview 15 CAMERA ROTATION

- Page 89 and 90:

System Overview 17 WORKSTATION CONT

- Page 91 and 92:

System Overview 19 A V E R A G I N

- Page 93 and 94:

System Overview 21 HELP PATIENT (AN

- Page 95 and 96:

System Overview 23 Trackpad Panels

- Page 97:

System Overview 25 Lenzar Hardcopy

- Page 100:

System Overview 27 CONTROL PANEL WA

- Page 103:

System Overview 29 WORKSTATION COVE

- Page 107:

System Overview 31 3. Pull the left

- Page 110:

System Overview 33 8. Remove the mo

- Page 114 and 115:

System Overview 35 2. Grasp the top

- Page 117 and 118:

System Overview 37 COMPONENT LOCATI

- Page 120 and 121:

System Overview 39 Mobile C-Arm Com

- Page 122 and 123:

System Overview 41 WORKSTATION COMP

- Page 124 and 125:

System Overview 43 Power/Motor Rela

- Page 126 and 127:

System Overview 45 IR Receiver PCB

- Page 129 and 130:

POWER DISTRIBUTION OVERVIEW The inf

- Page 131 and 132:

Power Distribution 3 WORKSTATION CI

- Page 133 and 134:

Power Distribution 5 WORKSTATION IS

- Page 135 and 136:

Power Distribution 7 POWER CONTROL

- Page 137 and 138: Power Distribution 9 F1 CB1 CB2 CB3

- Page 139 and 140: Power Distribution 11 PS4 (+24 VDC)

- Page 141 and 142: Power Distribution 13 Figure 8 DC P

- Page 144: Power Distribution 15 PS1 (5V and 1

- Page 147: Power Distribution 17 115VAC_PH_SW

- Page 150 and 151: Power Distribution 19 120 VAC DC 7

- Page 153: Power Distribution 21 S/N 69-1001 a

- Page 156 and 157: Power Distribution 23 L N 1 L D 1 G

- Page 158: Power Distribution 25 PS2 (24V) S/N

- Page 161 and 162: Power Distribution 27 Current Sensi

- Page 163 and 164: Power Distribution 29 Battery Charg

- Page 165 and 166: Power Distribution 31 S/N 69-1001 a

- Page 167 and 168: Power Distribution 33 Battery Charg

- Page 169 and 170: Power Distribution 35 BATTERY CHARG

- Page 171: 2 C-Arm Control • Mainframe Mothe

- Page 174 and 175: 4 C-Arm Control C-ARM WORKSTATION U

- Page 177 and 178: 6 C-Arm Control CONTROL PANEL PROCE

- Page 179: 8 C-Arm Control X-RAY SWITCH The si

- Page 182 and 183: 10 C-Arm Control This illustration

- Page 184 and 185: 12 C-Arm Control The functions of t

- Page 186 and 187: 14 C-Arm Control CARD RACK ASSEMBLI

- Page 190 and 191: 18 C-Arm Control 7-Segment Displays

- Page 193: 20 C-Arm Control ANALOG INTERFACE P

- Page 196 and 197: 22 C-Arm Control 9 6 2 U 1 U 1 8 R

- Page 199 and 200: 24 C-Arm Control A/D SECTION The A/

- Page 201: 26 C-Arm Control COUNTER/TIMER (CTC

- Page 204: 28 C-Arm Control BIT # PIN # SIGNAL

- Page 208 and 209: 30 C-Arm Control INTERLOCK SECTION

- Page 210: 32 C-Arm Control C-ARM MOTHERBOARD

- Page 213 and 214: 34 C-Arm Control 4 E 01E 1 J 1 2 1

- Page 215 and 216: 36 C-Arm Control Technique Processo

- Page 217 and 218: 38 C-Arm Control COMMUNICATION BETW

- Page 220 and 221: 2 C-Arm Software LOADING APPLICATIO

- Page 222 and 223: 4 C-Arm Software BOOT SEQUENCE Duri

- Page 224 and 225: 6 C-Arm Software X-RAY CONTROL PANE

- Page 226 and 227: 8 C-Arm Software A - Run Applicatio

- Page 229 and 230: 10 C-Arm Software C - Run Calibrati

- Page 232 and 233: 12 C-Arm Software H - Collimator Ca

- Page 234 and 235: 14 C-Arm Software SRAM FILES The fo

- Page 237 and 238: 16 C-Arm Software SRAM CARD COPY FI

- Page 239 and 240:

18 C-Arm Software HOT-BYTE INFORMAT

- Page 241 and 242:

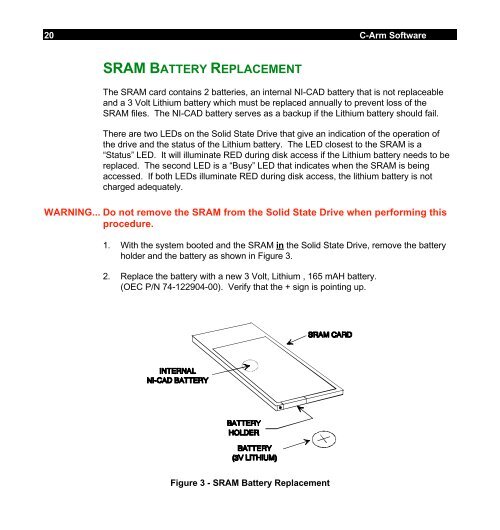

20 C-Arm Software SRAM BATTERY REPL

- Page 243 and 244:

2 Interlocks / Stator Power Signal

- Page 245 and 246:

4 Interlocks / Stator FAST STOP The

- Page 247:

6 Interlocks / Stator JUMPER E5/REL

- Page 250 and 251:

8 Interlocks / Stator NORMAL PRE-CH

- Page 253 and 254:

10 Interlocks / Stator STATOR START

- Page 255 and 256:

12 Interlocks / Stator BATTERY CHAR

- Page 257 and 258:

14 Interlocks / Stator POWER SUPPLY

- Page 259 and 260:

X-RAY ON/DISABLE OVERVIEW This sect

- Page 261:

X-ray On / Disable 3 X-RAY ENABLE S

- Page 264 and 265:

X-ray On / Disable 5 X-RAY DISABLE

- Page 267 and 268:

KV GENERATION OVERVIEW kV is regula

- Page 269 and 270:

kV Generation 3 The return path for

- Page 272 and 273:

kV Generation 5 KV ERROR CORRECTION

- Page 274 and 275:

kV Generation 7 Figure 3 kV Servo C

- Page 276 and 277:

kV Generation 9 KV GENERATOR FAULTS

- Page 278 and 279:

kV Generation 11 NOTE If the second

- Page 281:

kV Generation 13 KV ERROR CORRECTIO

- Page 284 and 285:

2 mA Generation CONTROL INPUTS The

- Page 286 and 287:

4 mA Generation FILAMENT REGULATOR

- Page 288 and 289:

6 mA Generation MA SENSE Detects th

- Page 290 and 291:

8 mA Generation MA ERROR LOOP EXAMP

- Page 292 and 293:

10 mA Generation Figure 2 - mA Serv

- Page 294:

12 mA Generation LOW FLUORO MA The

- Page 297:

14 mA Generation MA ERROR CORRECTIO

- Page 300 and 301:

2 Generator Calibration During the

- Page 302 and 303:

4 Generator Calibration CALIBRATION

- Page 305 and 306:

6 Generator Calibration EQUIPMENT S

- Page 307 and 308:

8 Generator Calibration 11. Observi

- Page 310 and 311:

10 Generator Calibration FLUORO RAD

- Page 312 and 313:

12 Generator Calibration ACCESS CAL

- Page 315 and 316:

14 Generator Calibration NOTE: DUTY

- Page 318 and 319:

16 Generator Calibration KV/MA TECH

- Page 320:

18 Generator Calibration MERGE EXIS

- Page 324 and 325:

20 Generator Calibration 5R THEORY

- Page 327:

22 Generator Calibration Example 3

- Page 331 and 332:

24 Generator Calibration 5R ABS TAB

- Page 333:

26 Generator Calibration 3. Increas

- Page 336:

28 Generator Calibration NOTE: You

- Page 339 and 340:

30 Generator Calibration B. mA limi

- Page 341:

32 Generator Calibration 19. Withou

- Page 345 and 346:

34 Generator Calibration 10R ABS TA

- Page 347 and 348:

36 Generator Calibration 10R ENTRAN

- Page 350:

MECHANICAL ASSEMBLIES OVERVIEW The

- Page 353 and 354:

Mechanical Assemblies 3 HORIZONTAL

- Page 355 and 356:

Mechanical Assemblies 5 MECHANICAL

- Page 357:

Mechanical Assemblies 7 HORIZONTAL

- Page 360 and 361:

Mechanical Assemblies 9 Figure 5 -

- Page 362:

Mechanical Assemblies 11 FLIP FLOP

- Page 365:

Mechanical Assemblies 13 C-ARM BEAR

- Page 368:

Mechanical Assemblies 15 WIG WAG BR

- Page 372 and 373:

Mechanical Assemblies 17 Figure 8 -

- Page 374 and 375:

Mechanical Assemblies 19 REAR CASTE

- Page 377 and 378:

Mechanical Assemblies 21 FRONT WHEE

- Page 380 and 381:

Mechanical Assemblies 23 REAR WHEEL

- Page 382:

Mechanical Assemblies 25 Older Mode

- Page 385 and 386:

Mechanical Assemblies 27 Older Mode

- Page 387 and 388:

Mechanical Assemblies 29 Shim Adjus

- Page 389 and 390:

Mechanical Assemblies 31 L-ARM ROTA

- Page 391 and 392:

Mechanical Assemblies 33 CROSS ARM

- Page 393 and 394:

Mechanical Assemblies 35 Figure 16

- Page 395 and 396:

Mechanical Assemblies 37 VERTICAL C

- Page 397:

Mechanical Assemblies 39 3. Remove

- Page 400:

2 Image System Mainframe Motherboar

- Page 403 and 404:

4 Image System IMAGE FUNCTION PCB S

- Page 405 and 406:

6 Image System INPUT/OUTPUT U17 and

- Page 407 and 408:

8 Image System COLLIMATOR OVERVIEW

- Page 409 and 410:

10 Image System IRIS MOTOR The coll

- Page 411:

12 Image System LEAF IN/OUT MOTOR T

- Page 414:

14 Image System LEAF ROTATION MOTOR

- Page 417 and 418:

16 Image System COLLIMATOR ERROR ME

- Page 419 and 420:

18 Image System IMAGE INTENSIFIER O

- Page 421 and 422:

20 Image System WARNING... Image in

- Page 423 and 424:

22 Image System CCD CAMERA OVERVIEW

- Page 425:

24 Image System Invert Image/ Rever

- Page 429 and 430:

26 Image System Input 1 Input 2 Ena

- Page 432 and 433:

28 Image System Input 3 Input 4 Ena

- Page 434 and 435:

30 Image System Anti-Vignetting A s

- Page 437 and 438:

32 Image System PIXEL/COLUMN FILTER

- Page 439:

34 Image System PIXEL FILTER PCB As

- Page 442 and 443:

36 Image System CCD CAMERA REPLACEM

- Page 444 and 445:

38 Image System CCD CAMERA REPLACEM

- Page 446 and 447:

40 Image System VIDEO LEVEL INDICAT

- Page 448 and 449:

42 Image System

- Page 450 and 451:

44 Image System STATOR THERMAL CUTO

- Page 452 and 453:

46 Image System REPLACEMENT OF HIGH

- Page 455 and 456:

IMAGE SYSTEM CALIBRATION The proced

- Page 457:

Image System Calibration 3 TOOLS Th

- Page 460 and 461:

Image System Calibration 5 4. Attac

- Page 463 and 464:

Image System Calibration 7 CALIBRAT

- Page 465:

Image System Calibration 9 10. With

- Page 468 and 469:

Image System Calibration 11 CONFIRM

- Page 470 and 471:

Image System Calibration 13 ADJUST

- Page 472:

Image System Calibration 15 8. Sele

- Page 475 and 476:

Image System Calibration 17 Figure

- Page 477:

Image System Calibration 19 4. If t

- Page 480:

Image System Calibration 21 0° 270

- Page 483:

Image System Calibration 23 ADJUST

- Page 486 and 487:

Image System Calibration 25 COLLIMA

- Page 488 and 489:

Image System Calibration 27 NOTE: I

- Page 491 and 492:

Image System Calibration 29 VARIABL

- Page 493 and 494:

Image System Calibration 31 9. Sele

- Page 495 and 496:

Image System Calibration 33 BEAM AL

- Page 497:

Image System Calibration 35 C. Swin

- Page 500 and 501:

Image System Calibration 37 Adjust

- Page 503 and 504:

Image System Calibration 39 PIXEL/C

- Page 506 and 507:

Image System Calibration 41 ANTI-VI

- Page 508 and 509:

OVERVIEW WORKSTATION CONTROL This s

- Page 510 and 511:

Workstation Control 3 CONTROL PANEL

- Page 512 and 513:

Workstation Control 5 CONTROL PANEL

- Page 515 and 516:

Workstation Control 7 Figure 3 - Wo

- Page 517 and 518:

Workstation Control 9 ELECTRONICS B

- Page 520 and 521:

Workstation Control 11 AUXILIARY IN

- Page 522 and 523:

Workstation Control 13 X-RAY DISABL

- Page 524 and 525:

Workstation Control 15 COMMUNICATIO

- Page 527:

Workstation Control 17 OPTION PROM

- Page 530:

Workstation Control 19 386 AT MOTHE

- Page 533 and 534:

Workstation Control 21 IR (INFRARED

- Page 535 and 536:

Workstation Control 23 If the pulse

- Page 538:

Workstation Control 25 IR RECEIVER

- Page 541 and 542:

Workstation Control 27 Older Style

- Page 544 and 545:

Workstation Control 29 INTERCONNECT

- Page 546 and 547:

2 Workstation Software WORKSTATION

- Page 549 and 550:

4 Workstation Software FRONT PANEL

- Page 551 and 552:

6 Workstation Software TOGGLE MOTIO

- Page 553 and 554:

8 Workstation Software Qwerty Keys

- Page 555 and 556:

10 Workstation Software Track Pad K

- Page 557 and 558:

12 Workstation Software Front Panel

- Page 559 and 560:

14 Workstation Software Tone Contro

- Page 561 and 562:

16 Workstation Software Watchdog Re

- Page 564 and 565:

Video Path 2 REFERENCE SCHEMATICS T

- Page 566 and 567:

Video Path 4 HIGH SCAN NON INTERLAC

- Page 568 and 569:

Video Path 6 WORKSTATION The video

- Page 570 and 571:

Video Path 8 Auxiliary Interface PC

- Page 572:

Video Path 10 Peripherals Analog in

- Page 576 and 577:

Video Path 12 HARD COPY CAMERA Vide

- Page 578 and 579:

Video Path 14 Auxiliary Interface P

- Page 580 and 581:

Video Path 16 Video Switching PCB O

- Page 582 and 583:

Video Path 18 Scan Converter PCB Fi

- Page 584 and 585:

2 Video Control IMAGE PROCESSOR PCB

- Page 587 and 588:

4 Video Control IMAGE PROCESSOR TES

- Page 589 and 590:

6 Video Control VIDEO SWITCHING PCB

- Page 591:

8 Video Control 50/60 HZ VIDEO CONT

- Page 594 and 595:

10 Video Control FAST SCAN MONITORS

- Page 596:

12 Video Control CONTRAST AND BRIGH

- Page 599 and 600:

14 Video Control HIGH SCAN BRIGHTNE

- Page 601 and 602:

2 Image Storage IDE HARD DISK DRIVE

- Page 603 and 604:

4 Image Storage 30FPS SCSI DISK OPT

- Page 605 and 606:

6 Image Storage 4/30 FPS SCSI DISK

- Page 607 and 608:

8 Image Storage 14. The following w

- Page 610 and 611:

Image Storage DEBUGGING USING IP-SC

- Page 613 and 614:

12 Image Storage Figure 5

- Page 615:

14 Image Storage Figure 7 - SCSI Di

- Page 618 and 619:

16 Image Storage Figure 9 - IP-SCSI

- Page 621 and 622:

18 Image Storage

- Page 623:

20 Image Storage J4 - NO JUMPERS TE

- Page 626 and 627:

2 Peripherals Figure 1 - Rear Panel

- Page 628 and 629:

4 Peripherals RECORD UNPROCESSED VI

- Page 630 and 631:

6 Peripherals VCR CONNECTIONS To en

- Page 632 and 633:

8 Peripherals HARD COPY CAMERA Imag

- Page 635 and 636:

10 Peripherals MOUNTING INFORMATION

- Page 637 and 638:

12 Peripherals DIGITAL LASER CAMERA

- Page 639:

14 Peripherals 6. When CUSTOMIZE OP

- Page 642 and 643:

16 Peripherals Digital Laser Camera

- Page 644 and 645:

18 Peripherals After the unit has b

- Page 646:

20 Peripherals 3. Then, select a sp

- Page 650:

22 Peripherals 4. Move the cursor t

- Page 653 and 654:

2 Appendix PAINT KITS PART NUMBER D

- Page 655 and 656:

4 Appendix SPECIFICATIONS & TOLERAN

- Page 658:

UPDATE 12-INCH IMAGE SYSTEM 9600 SY

- Page 662 and 663:

00 Imaging Workstation Service Manu

- Page 664:

9600 Imaging Workstation Service Ma

- Page 667 and 668:

9600 Imaging Workstation Service Ma

- Page 669:

9600 Imaging Workstation Service Ma

- Page 672 and 673:

9600 Imaging Workstation Service Ma

- Page 674:

9600 Imaging Workstation Service Ma

- Page 677 and 678:

9600 Imaging Workstation Service Ma

- Page 679:

9600 Imaging Workstation Service Ma

- Page 683 and 684:

9600 Imaging Workstation Service Ma

- Page 685:

9600 Imaging Workstation Service Ma