Calcul des etats atteignables de programmes Esterel partitionne ...

Calcul des etats atteignables de programmes Esterel partitionne ...

Calcul des etats atteignables de programmes Esterel partitionne ...

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

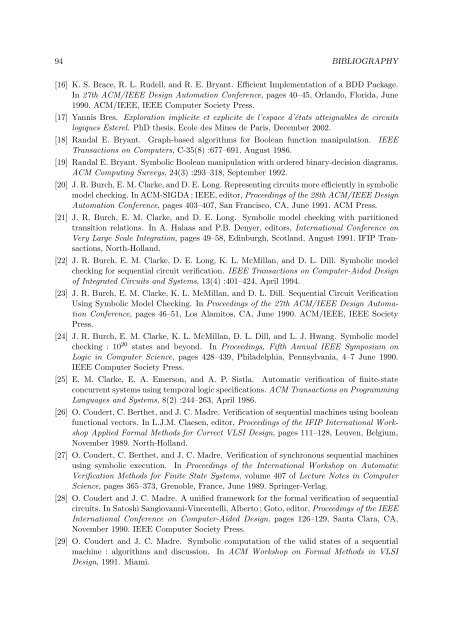

94 BIBLIOGRAPHY[16] K. S. Brace, R. L. Ru<strong>de</strong>ll, and R. E. Bryant. Efficient Implementation of a BDD Package.In 27th ACM/IEEE Design Automation Conference, pages 40–45, Orlando, Florida, June1990. ACM/IEEE, IEEE Computer Society Press.[17] Yannis Bres. Exploration implicite et explicite <strong>de</strong> l’espace d’états <strong>atteignables</strong> <strong>de</strong> circuitslogiques <strong>Esterel</strong>. PhD thesis, Ecole <strong><strong>de</strong>s</strong> Mines <strong>de</strong> Paris, December 2002.[18] Randal E. Bryant. Graph-based algorithms for Boolean function manipulation. IEEETransactions on Computers, C-35(8) :677–691, August 1986.[19] Randal E. Bryant. Symbolic Boolean manipulation with or<strong>de</strong>red binary-<strong>de</strong>cision diagrams.ACM Computing Surveys, 24(3) :293–318, September 1992.[20] J. R. Burch, E. M. Clarke, and D. E. Long. Representing circuits more efficiently in symbolicmo<strong>de</strong>l checking. In ACM-SIGDA ; IEEE, editor, Proceedings of the 28th ACM/IEEE DesignAutomation Conference, pages 403–407, San Francisco, CA, June 1991. ACM Press.[21] J. R. Burch, E. M. Clarke, and D. E. Long. Symbolic mo<strong>de</strong>l checking with partitionedtransition relations. In A. Halaas and P.B. Denyer, editors, International Conference onVery Large Scale Integration, pages 49–58, Edinburgh, Scotland, August 1991. IFIP Transactions,North-Holland.[22] J. R. Burch, E. M. Clarke, D. E. Long, K. L. McMillan, and D. L. Dill. Symbolic mo<strong>de</strong>lchecking for sequential circuit verification. IEEE Transactions on Computer-Ai<strong>de</strong>d Designof Integrated Circuits and Systems, 13(4) :401–424, April 1994.[23] J. R. Burch, E. M. Clarke, K. L. McMillan, and D. L. Dill. Sequential Circuit VerificationUsing Symbolic Mo<strong>de</strong>l Checking. In Proceedings of the 27th ACM/IEEE Design AutomationConference, pages 46–51, Los Alamitos, CA, June 1990. ACM/IEEE, IEEE SocietyPress.[24] J. R. Burch, E. M. Clarke, K. L. McMillan, D. L. Dill, and L. J. Hwang. Symbolic mo<strong>de</strong>lchecking : 10 20 states and beyond. In Proceedings, Fifth Annual IEEE Symposium onLogic in Computer Science, pages 428–439, Phila<strong>de</strong>lphia, Pennsylvania, 4–7 June 1990.IEEE Computer Society Press.[25] E. M. Clarke, E. A. Emerson, and A. P. Sistla. Automatic verification of finite-stateconcurrent systems using temporal logic specifications. ACM Transactions on ProgrammingLanguages and Systems, 8(2) :244–263, April 1986.[26] O. Cou<strong>de</strong>rt, C. Berthet, and J. C. Madre. Verification of sequential machines using booleanfunctional vectors. In L.J.M. Claesen, editor, Proceedings of the IFIP International WorkshopApplied Formal Methods for Correct VLSI Design, pages 111–128, Leuven, Belgium,November 1989. North-Holland.[27] O. Cou<strong>de</strong>rt, C. Berthet, and J. C. Madre. Verification of synchronous sequential machinesusing symbolic execution. In Proceedings of the International Workshop on AutomaticVerification Methods for Finite State Systems, volume 407 of Lecture Notes in ComputerScience, pages 365–373, Grenoble, France, June 1989. Springer-Verlag.[28] O. Cou<strong>de</strong>rt and J. C. Madre. A unified framework for the formal verification of sequentialcircuits. In Satoshi Sangiovanni-Vincentelli, Alberto ; Goto, editor, Proceedings of the IEEEInternational Conference on Computer-Ai<strong>de</strong>d Design, pages 126–129, Santa Clara, CA,November 1990. IEEE Computer Society Press.[29] O. Cou<strong>de</strong>rt and J. C. Madre. Symbolic computation of the valid states of a sequentialmachine : algorithms and discussion. In ACM Workshop on Formal Methods in VLSIDesign, 1991. Miami.