Script for Laboratory: Designing embedded ASIPs - CES

Script for Laboratory: Designing embedded ASIPs - CES

Script for Laboratory: Designing embedded ASIPs - CES

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

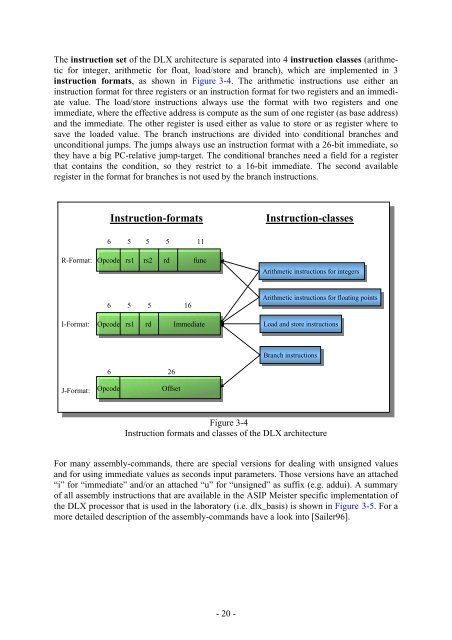

The instruction set of the DLX architecture is separated into 4 instruction classes (arithmetic<br />

<strong>for</strong> integer, arithmetic <strong>for</strong> float, load/store and branch), which are implemented in 3<br />

instruction <strong>for</strong>mats, as shown in Figure 3-4. The arithmetic instructions use either an<br />

instruction <strong>for</strong>mat <strong>for</strong> three registers or an instruction <strong>for</strong>mat <strong>for</strong> two registers and an immediate<br />

value. The load/store instructions always use the <strong>for</strong>mat with two registers and one<br />

immediate, where the effective address is compute as the sum of one register (as base address)<br />

and the immediate. The other register is used either as value to store or as register where to<br />

save the loaded value. The branch instructions are divided into conditional branches and<br />

unconditional jumps. The jumps always use an instruction <strong>for</strong>mat with a 26-bit immediate, so<br />

they have a big PC-relative jump-target. The conditional branches need a field <strong>for</strong> a register<br />

that contains the condition, so they restrict to a 16-bit immediate. The second available<br />

register in the <strong>for</strong>mat <strong>for</strong> branches is not used by the branch instructions.<br />

Instruction-<strong>for</strong>mats<br />

Instruction-<strong>for</strong>mats<br />

Instruction-classes<br />

Instruction-classes<br />

6 5 5 5 11<br />

6 5 5 5 11<br />

R-Format: Opcode rs1 rs2 rd func<br />

R-Format: Opcode rs1 rs2 rd func<br />

6 5 5 16<br />

6 5 5 16<br />

I-Format: Opcode rs1 rd Immediate<br />

I-Format: Opcode rs1 rd Immediate<br />

6 26<br />

6 26<br />

J-Format: Opcode Offset<br />

J-Format: Opcode Offset<br />

Arithmetic Arithmetic instructions<br />

Arithmetic instructions <strong>for</strong><br />

Arithmetic instructions <strong>for</strong> integers<br />

instructions <strong>for</strong> integers<br />

<strong>for</strong> integers integers<br />

Arithmetic Arithmetic instructions<br />

Arithmetic instructions <strong>for</strong><br />

Arithmetic instructions <strong>for</strong> floating<br />

instructions <strong>for</strong> floating points<br />

<strong>for</strong> floating points<br />

floating points points<br />

Load Load and<br />

Load and store<br />

Load and store instructions<br />

and store instructions<br />

store instructions instructions<br />

Branch Branch instructions<br />

Branch instructions<br />

Branch instructions instructions<br />

Figure 3-4<br />

Instruction <strong>for</strong>mats and classes of the DLX architecture<br />

For many assembly-commands, there are special versions <strong>for</strong> dealing with unsigned values<br />

and <strong>for</strong> using immediate values as seconds input parameters. Those versions have an attached<br />

“i” <strong>for</strong> “immediate” and/or an attached “u” <strong>for</strong> “unsigned” as suffix (e.g. addui). A summary<br />

of all assembly instructions that are available in the ASIP Meister specific implementation of<br />

the DLX processor that is used in the laboratory (i.e. dlx_basis) is shown in Figure 3-5. For a<br />

more detailed description of the assembly-commands have a look into [Sailer96].<br />

- 20 -