Script for Laboratory: Designing embedded ASIPs - CES

Script for Laboratory: Designing embedded ASIPs - CES

Script for Laboratory: Designing embedded ASIPs - CES

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

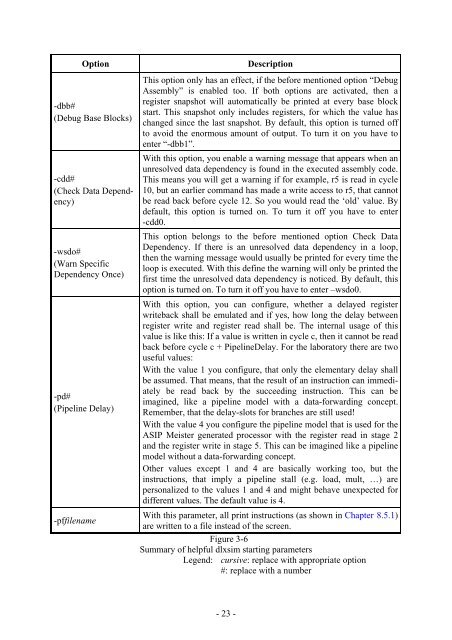

Option Description<br />

-dbb#<br />

(Debug Base Blocks)<br />

-cdd#<br />

(Check Data Dependency)<br />

-wsdo#<br />

(Warn Specific<br />

Dependency Once)<br />

-pd#<br />

(Pipeline Delay)<br />

-pffilename<br />

This option only has an effect, if the be<strong>for</strong>e mentioned option “Debug<br />

Assembly” is enabled too. If both options are activated, then a<br />

register snapshot will automatically be printed at every base block<br />

start. This snapshot only includes registers, <strong>for</strong> which the value has<br />

changed since the last snapshot. By default, this option is turned off<br />

to avoid the enormous amount of output. To turn it on you have to<br />

enter “-dbb1”.<br />

With this option, you enable a warning message that appears when an<br />

unresolved data dependency is found in the executed assembly code.<br />

This means you will get a warning if <strong>for</strong> example, r5 is read in cycle<br />

10, but an earlier command has made a write access to r5, that cannot<br />

be read back be<strong>for</strong>e cycle 12. So you would read the ‘old’ value. By<br />

default, this option is turned on. To turn it off you have to enter<br />

-cdd0.<br />

This option belongs to the be<strong>for</strong>e mentioned option Check Data<br />

Dependency. If there is an unresolved data dependency in a loop,<br />

then the warning message would usually be printed <strong>for</strong> every time the<br />

loop is executed. With this define the warning will only be printed the<br />

first time the unresolved data dependency is noticed. By default, this<br />

option is turned on. To turn it off you have to enter –wsdo0.<br />

With this option, you can configure, whether a delayed register<br />

writeback shall be emulated and if yes, how long the delay between<br />

register write and register read shall be. The internal usage of this<br />

value is like this: If a value is written in cycle c, then it cannot be read<br />

back be<strong>for</strong>e cycle c + PipelineDelay. For the laboratory there are two<br />

useful values:<br />

With the value 1 you configure, that only the elementary delay shall<br />

be assumed. That means, that the result of an instruction can immediately<br />

be read back by the succeeding instruction. This can be<br />

imagined, like a pipeline model with a data-<strong>for</strong>warding concept.<br />

Remember, that the delay-slots <strong>for</strong> branches are still used!<br />

With the value 4 you configure the pipeline model that is used <strong>for</strong> the<br />

ASIP Meister generated processor with the register read in stage 2<br />

and the register write in stage 5. This can be imagined like a pipeline<br />

model without a data-<strong>for</strong>warding concept.<br />

Other values except 1 and 4 are basically working too, but the<br />

instructions, that imply a pipeline stall (e.g. load, mult, …) are<br />

personalized to the values 1 and 4 and might behave unexpected <strong>for</strong><br />

different values. The default value is 4.<br />

With this parameter, all print instructions (as shown in Chapter 8.5.1)<br />

are written to a file instead of the screen.<br />

Figure 3-6<br />

Summary of helpful dlxsim starting parameters<br />

Legend: cursive: replace with appropriate option<br />

#: replace with a number<br />

- 23 -