Microcomputer Circuits and Processes

Microcomputer Circuits and Processes

Microcomputer Circuits and Processes

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

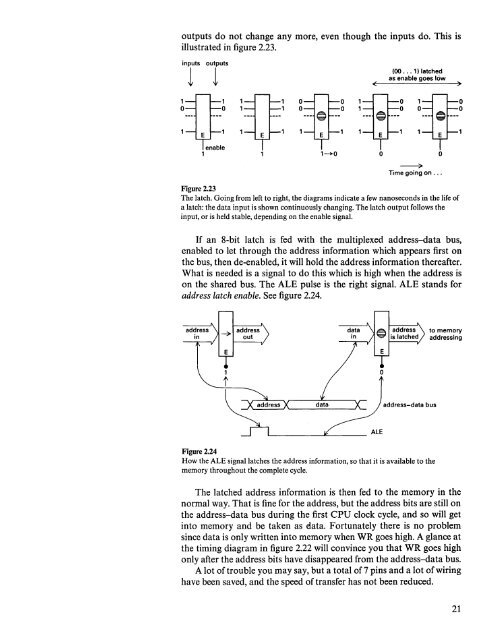

outputs do not change any more, even though the inputs do. This is<br />

illustrated in figure 2.23.<br />

T' our<br />

6~__<br />

___6<br />

1 E 1<br />

~*~ :*~*~<br />

(00... 1) latched<br />

as enable goes low<br />

(<br />

)<br />

:=fl=: ,-y-' ,-y-, ,-y-, ,-y-,<br />

enable<br />

1<br />

1 1-+0 0 0<br />

~<br />

Time going on ...<br />

Figure 2.23<br />

The latch. Going from left to right, the diagrams indicate a few nanoseconds in the life of<br />

a latch: the data input is shown continuously changing. The latch output follows the<br />

input, or is held stable, depending on the enable signal.<br />

If an 8-bit latch is fed with the multiplexed address-data bus,<br />

enabled to let through the address information which appears first on<br />

the bus, then de-enabled, it will hold the address information thereafter.<br />

What is needed is a signal to do this which is high when the address is<br />

on the shared bus. The ALE pulse is the right signal. ALE st<strong>and</strong>s for<br />

address latch enable. See figure 2.24.<br />

to memory<br />

addressing<br />

o<br />

address-data<br />

bus<br />

Figure 2.24<br />

How the ALE signal latches the address information, so that it is available to the<br />

memory throughout the complete cycle.<br />

The latched address information is then fed to the memory in the<br />

normal way. That is fine for the address, but the address bits are still on<br />

the address-data bus during the first CPU clock cycle, <strong>and</strong> so will get<br />

into memory <strong>and</strong> be taken as clata. Fortunately there is no problem<br />

since data is only written into memory when WR goes high. A glance at<br />

the timing diagram in figure 2.22 will convince you that WR goes high<br />

only after the address bits have disappeared from the address-data bus.<br />

A lot of trouble you may say, but a total of7 pins <strong>and</strong> a lot of wiring<br />

have been saved, <strong>and</strong> the speed of transfer has not been reduced.<br />

21