Microcomputer Circuits and Processes

Microcomputer Circuits and Processes

Microcomputer Circuits and Processes

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

a<br />

b<br />

The second FETCH cycle runs just like the first. Note the new value<br />

of the address on the bus (0010) since the program counter was<br />

incremented during the EXECUTE cycle.<br />

You should be able to see already a nice, organized pattern of data<br />

or address transfer <strong>and</strong> control signal variation. If you are feeling brave,<br />

why not complete a timing diagram for the entire program? If you do<br />

decide to have a go at completing the timing diagram, the following<br />

hints will be useful:<br />

Keep the ALE pulses appearing at regular intervals. Also keep RD (or<br />

WR) pulses appearing at regular intervals.<br />

During EXECUTE cycles 2 <strong>and</strong> 5, there is no increment in the program<br />

counter. Program counter increments are performed during clock<br />

period 2 of both FETCH <strong>and</strong> EXECUTE cycles, so EXECUTE cycles 2<br />

<strong>and</strong> 5 must look like any other EXECUTE cycle, except that clock<br />

period 2 is a 'dummy', <strong>and</strong> the actual executing takes place, as usual,<br />

during the third clock period.<br />

I hope you have got an impression of a lot of organized timings <strong>and</strong><br />

efficiency behind this simple program. An integrated-circuit microprocessor<br />

system is certainly integrated in more ways than one! Just how<br />

real is SAM? Quite real: it is possible to build a machine that will work<br />

just as described. The CPU 'architecture', how many registers, <strong>and</strong> how<br />

they are connected on the CPU chip, is probably underdeveloped in<br />

SAM; a typical 8-bit CPU chip will have seven or eight 16-bit registers,<br />

<strong>and</strong> a 16-bit CPU has to have a very sophisticated architecture. In their<br />

instruction sets, these processors may have tens of instructions dedicated<br />

to moving data between registers. And of course we have not<br />

talked about input-output. Different manufacturers have various<br />

philosophies of CPU architecture, but the notions we have been<br />

discussing, such as RD, WR, ALE, <strong>and</strong> the work in this chapter are<br />

common to most.<br />

The CPU has executed<br />

a STOP<br />

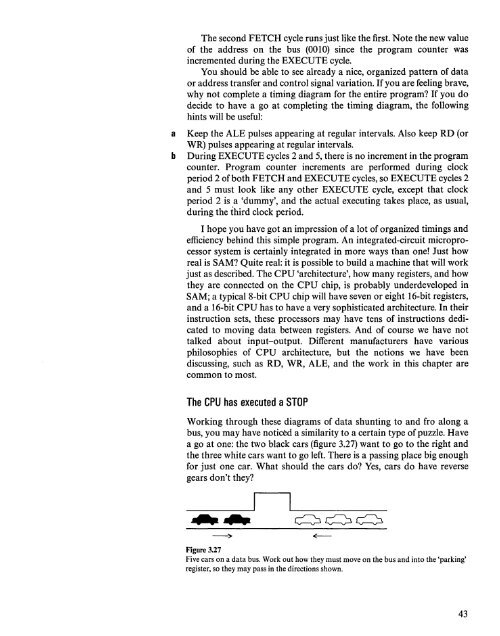

Working through these diagrams of data shunting to <strong>and</strong> fro along a<br />

bus, you may have noticed a similarity to a certain type of puzzle. Have<br />

a go at one: the two black cars (figure 3.27) want to go to the right <strong>and</strong><br />

the three white cars want to go left. There is a passing place big enough<br />

for just one car. What should the cars do? Yes, cars do have reverse<br />

gears don't they?<br />

,---<br />

____<br />

I<br />

.--- .---<br />

~~~<br />

Figure 3.27<br />

Five cars on a data bus. Work out how they must move on the bus <strong>and</strong> into the 'parking'<br />

register, so they may pass in the directions shown.<br />

43