- Page 1 and 2:

MEMORYDATABOOK1986

- Page 4 and 5:

CONTENTSo IC MEMORY LINE-UP AND TYP

- Page 6:

MSM28201 AASMSM53256RSMSK531000RS

- Page 10 and 11:

IC MEMORY LINE-UP AND TYPICALCHARAC

- Page 12 and 13:

---------.IC MEMORY LINE-UP AND TYP

- Page 14 and 15:

---------I.IC MEMORY LINE-UP AND TY

- Page 16:

----------_IC MEMORY LINE-UP AND TY

- Page 20 and 21:

PACKAGINGPACKAGESNo. RS GS JS US YS

- Page 22 and 23:

-----------------------------------

- Page 24 and 25: ~----------------------------------

- Page 26 and 27: -----------------------------------

- Page 28 and 29: ------------------.PACKAGING ••

- Page 31 and 32: oIIIRELIABILITY INFORMATION .......

- Page 33 and 34: I\JOl~rt-ProcessmentAcceptanceof or

- Page 35 and 36: • RELIABILITY INFORMATION ••

- Page 37 and 38: • RELIABILITY INFORMATION ••

- Page 39 and 40: • RELIABILITY INFORMATION .'-----

- Page 41 and 42: D MOS MEMORY HANDLING PRECAUTIONS .

- Page 45 and 46: D EPROM WRITING AND ERASURE .......

- Page 47: • EPROM WRITING AND ERASURE •

- Page 50 and 51: MASK ROM CUSTOMER PROGRAMSPECIFICAT

- Page 53 and 54: DD MASK ROM DEVELOPMENT FLOWCHART..

- Page 57 and 58: D TERMINOLOGY AND SYMBOLS .........

- Page 59 and 60: .TERMINOLOGYANDSyMBOLS.------------

- Page 61 and 62: • TERMINOLOGY AND SYMBOLS ... ---

- Page 63: _TERMINOLOGY AND SYMBOLS _._-------

- Page 66 and 67: MOSDYNAMICRAMS

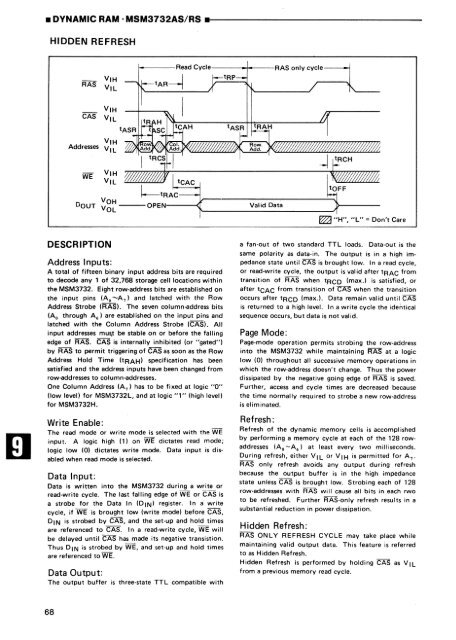

- Page 68 and 69: ----------------... DYNAMIC RAM· M

- Page 70 and 71: ----------------.... DYNAMIC RAM .

- Page 72 and 73: ----------------.... DYNAMIC RAM·

- Page 76 and 77: ________________... DYNAMIC RAM . M

- Page 78 and 79: ----------------... DYNAMIC RAM· M

- Page 80 and 81: ----------------... DYNAMIC RAM· M

- Page 82 and 83: _________________ • DYNAMIC RAM·

- Page 84 and 85: --------------------11. DYNAMIC RAM

- Page 86 and 87: ----------------... DYNAMIC RAM . M

- Page 88: ----------------__• DYNAMIC RAM'

- Page 91 and 92: • DYNAMIC RAM . MSM3764AS/RS .1--

- Page 93 and 94: • DYNAMIC RAM· MSM3764AS/RS •

- Page 95 and 96: • DYNAMIC RAM· MSM3764AS/RS •

- Page 97 and 98: • DYNAMIC RAM· MSM3764AS/RS •

- Page 99 and 100: OKI semiconductorMSM3764 AAS/RS65,5

- Page 101 and 102: • DYNAMIC RAM· MSM3764AAS/RS •

- Page 103 and 104: • DYNAMIC RAM· MSM3764AAS/RS •

- Page 105 and 106: • DYNAMIC RAM· MSM3764AAS/RS •

- Page 107 and 108: • DYNAMIC RAM· MSM3764AAS/RS •

- Page 109 and 110: • DYNAMIC RAM· MSM3764AAS/RS .--

- Page 111 and 112: • DYNAMIC RAM· MSM3764AAS/RS .--

- Page 113 and 114: • DYNAMIC RAM· MSM3764AAS/RS •

- Page 115 and 116: OKI semiconductorMSM41256AS/RS26214

- Page 117 and 118: • DYNAMIC RAM· MSM41256AS/RS •

- Page 119 and 120: • DYNAMIC RAM· MSM41256AS/RS .--

- Page 121 and 122: • DYNAMIC RAM· MSM41256AS/RS .1-

- Page 123 and 124: • DYNAMIC RAM· MSM41256AS/RS .--

- Page 125 and 126:

• DYNAMIC RAM· MSM41256AS/RS .--

- Page 127 and 128:

• DYNAMIC RAM· MSM41256AS/RS .-.

- Page 129 and 130:

OKI semiconductorMSM41256JS262144-B

- Page 131 and 132:

• DYNAMIC RAM·MSM41256JS ••

- Page 133 and 134:

_ DYNAMIC RAM· MSM41256JS _...._--

- Page 135 and 136:

• DYNAMIC RAM ·MSM41256JS .I----

- Page 137 and 138:

• DYNAMIC RAM· MSM41256JS ••

- Page 139 and 140:

OKI semiconductorMSM41 256AAS/RS262

- Page 141 and 142:

• DYNAMIC RAM· MSM41256AAS/RS .-

- Page 143 and 144:

• DYNAMIC RAM· MSM41256AAS/RS .-

- Page 145 and 146:

• DYNAMIC RAM· MSM41256AAS/RS .-

- Page 147 and 148:

• DYNAMIC RAM· MSM41256AAS/RS .1

- Page 149 and 150:

• DYNAMIC RAM· MSM41256AAS/RS .,

- Page 151 and 152:

• DYNAMIC RAM· MSM41256AAS/RS .1

- Page 153 and 154:

• DYNAMIC RAM· MSM41256AAS/RS .-

- Page 155 and 156:

.DYNAMICRAM·MSM41257AAS/RS.-------

- Page 157 and 158:

• DYNAMIC RAM· MSM41257 AAS/RS .

- Page 159 and 160:

• DYNAMIC RAM ·MSM41257AAS/RS .-

- Page 161 and 162:

• DYNAMIC RAM· MSM41257 AAS/RS .

- Page 163 and 164:

• DYNAMIC RAM ·MSM41257AAS/RS .-

- Page 165 and 166:

• DYNAMIC RAM· MSM41257AAS/RS .-

- Page 167 and 168:

• DYNAMIC RAM ·MSM41257AAS/RS .-

- Page 169 and 170:

• DYNAMIC RAM ·MSM41257AAS/RS .-

- Page 171 and 172:

• DYNAMIC RAM· MSM41464RS ••

- Page 173 and 174:

• DYNAMIC RAM· MSM41464RS ... --

- Page 175 and 176:

• DYNAMIC RAM· MSM41464RS .-----

- Page 177 and 178:

• DYNAMIC RAM· MSM41464RS ••

- Page 179 and 180:

.OVNAMICRAM·MSM41464RS.-----------

- Page 181 and 182:

• DYNAMIC RAM ·MSM41464RS .1----

- Page 183 and 184:

• DYNAMIC RAM' MSM41464RS .------

- Page 185 and 186:

.---=D=-._K __ I __s_._rn-'----l_c_

- Page 187 and 188:

• DYNAMIC RAM· MSM414256RS .----

- Page 189 and 190:

• DYNAMIC RAM • MSM414256RS .--

- Page 191 and 192:

• DYNAMIC RAM 'MSM414256RS .-----

- Page 193 and 194:

• DYNAMIC RAM . MSM414256RS .1---

- Page 195 and 196:

• DYNAMIC RAM . MSM414256RS .1---

- Page 197 and 198:

• DYNAMIC RAM· MSM414256RS •

- Page 199 and 200:

_ DYNAMIC RAM· MSM411 OOORS ___ --

- Page 201 and 202:

• DYNAMIC RAM· MSM411 OOORS •

- Page 203 and 204:

• DYNAMIC RAM· MSM411 OOORS •

- Page 205 and 206:

• DYNAMIC RAM· MSM411 OOORS ...

- Page 207 and 208:

• DYNAMIC RAM· MSM411 OOORS •

- Page 209 and 210:

• DYNAMIC RAM· MSM411 OOORS •

- Page 211 and 212:

OKI semiconductorMSM411 001 RS10485

- Page 213 and 214:

• DYNAMIC RAM· MSM411 001 RS .--

- Page 215 and 216:

• DYNAMIC RAM· MSM411001 RS •

- Page 217 and 218:

• DYNAMIC RAM· MSM411 001 RS .--

- Page 219 and 220:

_ DYNAMIC RAM· MSM411 001 RS ___ -

- Page 221 and 222:

• DYNAMIC RAM' MSM411 001 RS •

- Page 223 and 224:

• DYNAMIC RAM· MSM411 001 RS .1-

- Page 225 and 226:

OKI semiconductor ~----------------

- Page 227 and 228:

O __ K __ I __ seMSM514257RS__ rn_I

- Page 229 and 230:

• DYNAMIC RAM· MSM37S64ARS/37S64

- Page 231 and 232:

• DYNAMIC RAM· MSM37S64ARS/37S64

- Page 233 and 234:

• DYNAMIC RAM· MSM37S64ARS/37S64

- Page 235 and 236:

• DYNAMIC RAM· MSM37S64ARS/37S64

- Page 237 and 238:

_ DYNAMIC RAM· MSM37S64ARS/37S64RS

- Page 239 and 240:

• DYNAMIC RAM· MSM37S64ARS/37S64

- Page 241 and 242:

_O_K __ I __se_rn_I_C_O_nc:I_U_c_.o

- Page 243 and 244:

• DYNAMIC RAM· MSC2301 YS9/KS9 .

- Page 245 and 246:

_ DYNAMIC RAM· MSC2301 YS9/KS9 ---

- Page 247 and 248:

• DYNAMIC RAM· MSC2301 YS9/KS9

- Page 249 and 250:

• DYNAMIC RAM· MSC2301 YS9/KS9 .

- Page 251 and 252:

• DYNAMIC RAM· MSC2301 YS9/KS9 .

- Page 253 and 254:

• DYNAMIC RAM· MSC2304YSS/KSS .1

- Page 255 and 256:

.DYNAMICRAM·MSC2304YSS/KSS.-------

- Page 257:

• DYNAMIC RAM· MSC2304YSS/KSS .1

- Page 260 and 261:

_______________.... DYNAMIC RAM· M

- Page 262 and 263:

---------------..... DYNAMIC RAM·

- Page 264 and 265:

----------------1. DYNAMIC RAM· MS

- Page 266 and 267:

----------------. DYNAMIC RAM· MSC

- Page 268 and 269:

---------------1. DYNAMIC RAM· MSC

- Page 270 and 271:

------------------------------___ O

- Page 272 and 273:

-----------------11. DYNAMIC RAM·

- Page 274 and 275:

MOSSTATICRAMS

- Page 276 and 277:

------------------1. STATIC RAM ·M

- Page 278 and 279:

-------------------1. STATIC RAM·

- Page 280 and 281:

OKI semiconductorMSM2128RS2 KW x 8

- Page 282 and 283:

-------------------11. STATIC RAM

- Page 284 and 285:

-------------------11. STATIC RAM

- Page 286 and 287:

_______.,..--__________-11. STATIC

- Page 288 and 289:

-------------------. STATIC RAM 'MS

- Page 290 and 291:

OKI semiconductorMSM5128 - 20GSK204

- Page 292 and 293:

-----------------. STATIC RAM· MSM

- Page 294 and 295:

-----------------. STATIC RAM· MSM

- Page 296 and 297:

OKI semiconductorMSM5126RS2048-WORD

- Page 298 and 299:

-------------------. STATIC RAM 'MS

- Page 300 and 301:

-------------------. STATIC RAM ·M

- Page 302 and 303:

------------------. STATIC RAM· MS

- Page 304 and 305:

------------------. STATIC RAM· MS

- Page 306 and 307:

-----------------11. STATIC RAM· M

- Page 308 and 309:

-----------------1. STATIC RAM· MS

- Page 310 and 311:

-----------------1. STATIC RAM· MS

- Page 312 and 313:

-----------------... STATIC RAM ·M

- Page 314 and 315:

o __ K__ I __MSM5188USse_rn_IC_O_nc

- Page 316 and 317:

--------------------11. STATIC RAM

- Page 318 and 319:

___________________ • STATIC RAM

- Page 320 and 321:

-----------------. STATIC RAM' MSM5

- Page 322 and 323:

-----------------. STATIC RAM ·MSM

- Page 324 and 325:

-----------------. STATIC RAM' MSM5

- Page 326 and 327:

----------------1. STATIC RAM· MSM

- Page 328 and 329:

-----------------I.STATICRAM·MSM51

- Page 330 and 331:

----------------... STATIC RAM· MS

- Page 332 and 333:

MOSMASKROMS

- Page 334 and 335:

-----------------------------------

- Page 336 and 337:

------------------___ • MASK ROM

- Page 338 and 339:

-----------------__._ MASK ROM ·MS

- Page 340 and 341:

-----------------------------------

- Page 342 and 343:

------------------.... MASK ROM . M

- Page 344 and 345:

------------------.... MASK ROM . M

- Page 346 and 347:

-----------------_____ MASK ROM· M

- Page 348 and 349:

-----------------____ MASK ROM . MS

- Page 350 and 351:

------------------..... MASK ROM ·

- Page 352 and 353:

-----------------------------------

- Page 354 and 355:

-----------------_____ MASK ROM· M

- Page 356 and 357:

------------------___ MASK ROM· MS

- Page 358 and 359:

OKI semiconductorMSM28201AAS1M BIT

- Page 360 and 361:

-----------------------------------

- Page 362 and 363:

-----------------------------------

- Page 364 and 365:

-----------------------------------

- Page 366 and 367:

___________________________________

- Page 368 and 369:

-----------------------------------

- Page 370:

-----------------____ MASK ROM . MS

- Page 373 and 374:

OKI semiconductorMSM2764AS8192 x 8

- Page 375 and 376:

.EPROM·MSM2764AS •• ----------

- Page 377 and 378:

.EPROM·MSM2764AS.I----------------

- Page 379 and 380:

OKI semiconductorMSM27128AS16384 x

- Page 381 and 382:

.EPROM·MSM27128AS •• ---------

- Page 383 and 384:

.EPROM·MSM27128AS •• ---------

- Page 385 and 386:

OKI semiconductorMSM27256AS32768 x

- Page 387 and 388:

.EPROM·MSM27256AS •• ---------

- Page 389 and 390:

.EPROM·MSM27256AS •• ---------

- Page 391 and 392:

OKI semiconductorMSM27512AS65536 x

- Page 393 and 394:

.EPROM·MSM27512AS •• ---------

- Page 395 and 396:

.EPROM·MSM27512AS.--------~-------

- Page 397 and 398:

.EPROM·MSM271000AS •.-----------

- Page 399 and 400:

.EPROM·MSM271000AS •• --------

- Page 401 and 402:

.EPROM·MSM271000AS •• --------

- Page 403 and 404:

.EPROM·MSM271024AS.---------------

- Page 405 and 406:

.EPROM·MSM271024AS.I--------------

- Page 407 and 408:

.EPROM·MSM271024AS •• --------

- Page 409 and 410:

.EPROM·MSM27C64AS •• ---------

- Page 411 and 412:

_EPROM·MSM27C64AS ___ ------------

- Page 413 and 414:

_EPROM·MSM27C64AS_._--------------

- Page 415 and 416:

.EPROM·MSM27C128AS .--------------

- Page 417 and 418:

.EPROM·MSM27C128AS.I--------------

- Page 419 and 420:

.EPROM·MSM27C128AS •• --------

- Page 421 and 422:

_EPROM·MSM27C1024AS ___ ----------

- Page 423 and 424:

.EPROM·MSM27C1024AS.--------------

- Page 425 and 426:

_EPROM·MSM27C1024AS-.-------------

- Page 427 and 428:

OKI semiconductorMSM2816ARS2K x 8 B

- Page 429 and 430:

.EEPROM·MSM2816ARS.I--------------

- Page 431 and 432:

.EEPROM·MSM2816ARS.---------------

- Page 433 and 434:

·EEPROM·MSM2816ARS.I-------------

- Page 437 and 438:

IIi) CROSS REFERENCE LIST1. DYNAMIC

- Page 439 and 440:

....Co)I\JStructureTotalBit§ori_\

- Page 441 and 442:

~c.J~NMOSTotalBit1M§StructureOr- N

- Page 443 and 444:

.l>e,)Ol§2. STATIC RAMStruc- Total

- Page 445 and 446:

.....U)(Xl3. MASK ROM§Or- NumtureB

- Page 447 and 448:

~~oNMOSTotaLBit256k512k§StructureO

- Page 451 and 452:

m APPLICATIONS64K BIT DYNAMIC RAM A

- Page 453 and 454:

• APPLICATIONS •• -----------

- Page 455 and 456:

_APPLICATIONS __ -------------_____

- Page 457 and 458:

• APPLICATIONS •• -----------

- Page 459 and 460:

• APPLICATIONS •• -----------

- Page 461 and 462:

CMOS RAM BATTERY BACK-UPA practical

- Page 463 and 464:

• APPLICATIONS •• -----------

- Page 465 and 466:

MASK ROM KANJI GENERATION MEMORYDES

- Page 467 and 468:

_APPLICATIONS _a_------____________

- Page 469 and 470:

• APPLICATIONS •• -----------

- Page 471 and 472:

• APPLICATIONS ... --------------