PCT/2001/45 - World Intellectual Property Organization

PCT/2001/45 - World Intellectual Property Organization

PCT/2001/45 - World Intellectual Property Organization

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

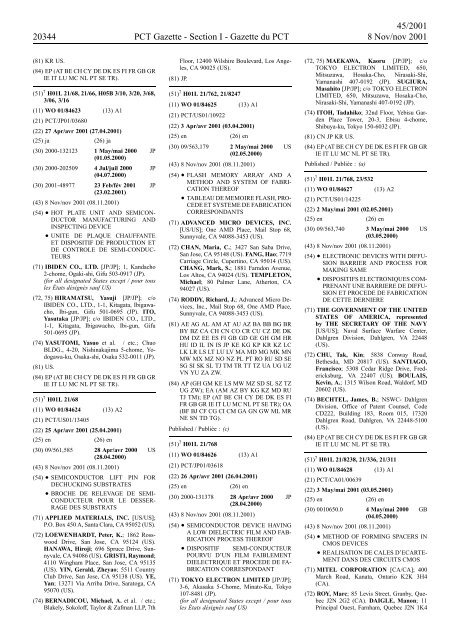

<strong>45</strong>/<strong>2001</strong><br />

20344 <strong>PCT</strong> Gazette - Section I - Gazette du <strong>PCT</strong> 8 Nov/nov <strong>2001</strong><br />

(81) KR US.<br />

(84) EP (AT BE CH CY DE DK ES FI FR GB GR<br />

IE IT LU MC NL PT SE TR).<br />

(51) 7 H01L 21/68, 21/66, H05B 3/10, 3/20, 3/68,<br />

3/06, 3/16<br />

(11) WO 01/84623<br />

(21) <strong>PCT</strong>/JP01/03680<br />

(13) A1<br />

(22) 27 Apr/avr <strong>2001</strong> (27.04.<strong>2001</strong>)<br />

(25) ja (26) ja<br />

(30) 2000-132123 1 May/mai 2000<br />

(01.05.2000)<br />

JP<br />

(30) 2000-202509 4 Jul/juil 2000<br />

(04.07.2000)<br />

JP<br />

(30) <strong>2001</strong>-48977 23 Feb/fév <strong>2001</strong><br />

(23.02.<strong>2001</strong>)<br />

JP<br />

(43) 8 Nov/nov <strong>2001</strong> (08.11.<strong>2001</strong>)<br />

(54) HOT PLATE UNIT AND SEMICON-<br />

DUCTOR MANUFACTURING AND<br />

INSPECTING DEVICE<br />

UNITE DE PLAQUE CHAUFFANTE<br />

ET DISPOSITIF DE PRODUCTION ET<br />

DE CONTROLE DE SEMI-CONDUC-<br />

TEURS<br />

(71) IBIDEN CO., LTD. [JP/JP]; 1, Kandacho<br />

2-chome, Ogaki-shi, Gifu 503-0917 (JP).<br />

(for all designated States except / pour tous<br />

les États désignés sauf US)<br />

(72, 75) HIRAMATSU, Yasuji [JP/JP]; c/o<br />

IBIDEN CO., LTD., 1-1, Kitagata, Ibigawacho,<br />

Ibi-gun, Gifu 501-0695 (JP). ITO,<br />

Yasutaka [JP/JP]; c/o IBIDEN CO., LTD.,<br />

1-1, Kitagata, Ibigawacho, Ibi-gun, Gifu<br />

501-0695 (JP).<br />

(74) YASUTOMI, Yasuo et al. / etc.; Chuo<br />

BLDG., 4-20, Nishinakajima 5-chome, Yodogawa-ku,<br />

Osaka-shi, Osaka 532-0011 (JP).<br />

(81) US.<br />

(84) EP (AT BE CH CY DE DK ES FI FR GB GR<br />

IE IT LU MC NL PT SE TR).<br />

(51) 7 H01L 21/68<br />

(11) WO 01/84624 (13) A2<br />

(21) <strong>PCT</strong>/US01/13405<br />

(22) 25 Apr/avr <strong>2001</strong> (25.04.<strong>2001</strong>)<br />

(25) en (26) en<br />

(30) 09/561,585 28 Apr/avr 2000 US<br />

(28.04.2000)<br />

(43) 8 Nov/nov <strong>2001</strong> (08.11.<strong>2001</strong>)<br />

(54) SEMICONDUCTOR LIFT PIN FOR<br />

DECHUCKING SUBSTRATES<br />

BROCHE DE RELEVAGE DE SEMI-<br />

CONDUCTEUR POUR LE DESSER-<br />

RAGE DES SUBSTRATS<br />

(71) APPLIED MATERIALS, INC. [US/US];<br />

P.O. Box <strong>45</strong>0 A, Santa Clara, CA 95052 (US).<br />

(72) LOEWENHARDT, Peter, K.; 1862 Rosswood<br />

Drive, San Jose, CA 95124 (US).<br />

HANAWA, Hiroji; 696 Spruce Drive, Sunnyvale,<br />

CA 94086 (US). GRISTI, Raymond;<br />

4110 Wingham Place, San Jose, CA 95135<br />

(US). YIN, Gerald, Zheyao; 5511 Country<br />

Club Drive, San Jose, CA 95138 (US). YE,<br />

Yan; 13271 Via Arriba Drive, Saratoga, CA<br />

95070 (US).<br />

(74) BERNADICOU, Michael, A. et al. / etc.;<br />

Blakely, Sokoloff, Taylor & Zafman LLP, 7th<br />

Floor, 12400 Wilshire Boulevard, Los Angeles,<br />

CA 90025 (US).<br />

(81) JP.<br />

(51) 7 H01L 21/762, 21/8247<br />

(11) WO 01/84625 (13) A1<br />

(21) <strong>PCT</strong>/US01/10922<br />

(22) 3 Apr/avr <strong>2001</strong> (03.04.<strong>2001</strong>)<br />

(25) en (26) en<br />

(30) 09/563,179 2 May/mai 2000 US<br />

(02.05.2000)<br />

(43) 8 Nov/nov <strong>2001</strong> (08.11.<strong>2001</strong>)<br />

(54) FLASH MEMORY ARRAY AND A<br />

METHOD AND SYSTEM OF FABRI-<br />

CATION THEREOF<br />

TABLEAU DE MEMOIRE FLASH, PRO-<br />

CEDE ET SYSTEME DE FABRICATION<br />

CORRESPONDANTS<br />

(71) ADVANCED MICRO DEVICES, INC.<br />

[US/US]; One AMD Place, Mail Stop 68,<br />

Sunnyvale, CA 94088-3<strong>45</strong>3 (US).<br />

(72) CHAN, Maria, C.; 3427 San Saba Drive,<br />

San Jose, CA 95148 (US). FANG, Hao; 7719<br />

Carriage Circle, Cupertino, CA 95014 (US).<br />

CHANG, Mark, S.; 1881 Farndon Avenue,<br />

Los Altos, CA 94024 (US). TEMPLETON,<br />

Michael; 80 Palmer Lane, Atherton, CA<br />

94027 (US).<br />

(74) RODDY, Richard, J.; Advanced Micro Devices,<br />

Inc., Mail Stop 68, One AMD Place,<br />

Sunnyvale, CA 94088-3<strong>45</strong>3 (US).<br />

(81) AE AG AL AM AT AU AZ BA BB BG BR<br />

BY BZ CA CH CN CO CR CU CZ DE DK<br />

DM DZ EE ES FI GB GD GE GH GM HR<br />

HU ID IL IN IS JP KE KG KP KR KZ LC<br />

LK LR LS LT LU LV MA MD MG MK MN<br />

MW MX MZ NO NZ PL PT RO RU SD SE<br />

SG SI SK SL TJ TM TR TT TZ UA UG UZ<br />

VN YU ZA ZW.<br />

(84) AP (GH GM KE LS MW MZ SD SL SZ TZ<br />

UG ZW); EA (AM AZ BY KG KZ MD RU<br />

TJ TM); EP (AT BE CH CY DE DK ES FI<br />

FR GB GR IE IT LU MC NL PT SE TR); OA<br />

(BF BJ CF CG CI CM GA GN GW ML MR<br />

NE SN TD TG).<br />

Published / Publiée :(c)<br />

(51) 7 H01L 21/768<br />

(11) WO 01/84626<br />

(21) <strong>PCT</strong>/JP01/03618<br />

(13) A1<br />

(22) 26 Apr/avr <strong>2001</strong> (26.04.<strong>2001</strong>)<br />

(25) en (26) en<br />

(30) 2000-131378 28 Apr/avr 2000<br />

(28.04.2000)<br />

JP<br />

(43) 8 Nov/nov <strong>2001</strong> (08.11.<strong>2001</strong>)<br />

(54) SEMICONDUCTOR DEVICE HAVING<br />

A LOW DIELECTRIC FILM AND FAB-<br />

RICATION PROCESS THEREOF<br />

DISPOSITIF SEMI-CONDUCTEUR<br />

POURVU D’UN FILM FAIBLEMENT<br />

DIELECTRIQUE ET PROCEDE DE FA-<br />

BRICATION CORRESPONDANT<br />

(71) TOKYO ELECTRON LIMITED [JP/JP];<br />

3-6, Akasaka 5-Chome, Minato-Ku, Tokyo<br />

107-8481 (JP).<br />

(for all designated States except / pour tous<br />

les États désignés sauf US)<br />

(72, 75) MAEKAWA, Kaoru [JP/JP]; c/o<br />

TOKYO ELECTRON LIMITED, 650,<br />

Mitsuzawa, Hosaka-Cho, Nirasaki-Shi,<br />

Yamanashi 407-0192 (JP). SUGIURA,<br />

Masahito [JP/JP]; c/o TOKYO ELECTRON<br />

LIMITED, 650, Mitsuzawa, Hosaka-Cho,<br />

Nirasaki-Shi, Yamanashi 407-0192 (JP).<br />

(74) ITOH, Tadahiko; 32nd Floor, Yebisu Garden<br />

Place Tower, 20-3, Ebisu 4-chome,<br />

Shibuya-ku, Tokyo 150-6032 (JP).<br />

(81) CN JP KR US.<br />

(84) EP (AT BE CH CY DE DK ES FI FR GB GR<br />

IE IT LU MC NL PT SE TR).<br />

Published / Publiée :(a)<br />

(51) 7 H01L 21/768, 23/532<br />

(11) WO 01/84627<br />

(21) <strong>PCT</strong>/US01/14225<br />

(13) A2<br />

(22) 2 May/mai <strong>2001</strong> (02.05.<strong>2001</strong>)<br />

(25) en (26) en<br />

(30) 09/563,740 3 May/mai 2000<br />

(03.05.2000)<br />

US<br />

(43) 8 Nov/nov <strong>2001</strong> (08.11.<strong>2001</strong>)<br />

(54) ELECTRONIC DEVICES WITH DIFFU-<br />

SION BARRIER AND PROCESS FOR<br />

MAKING SAME<br />

DISPOSITIFS ELECTRONIQUES COM-<br />

PRENANT UNE BARRIERE DE DIFFU-<br />

SION ET PROCEDE DE FABRICATION<br />

DE CETTE DERNIERE<br />

(71) THE GOVERNMENT OF THE UNITED<br />

STATES OF AMERICA, represented<br />

by THE SECRETARY OF THE NAVY<br />

[US/US]; Naval Surface Warfare Center,<br />

Dahlgren Division,<br />

(US).<br />

Dahlgren, VA 22448<br />

(72) CHU, Tak, Kin; 5838 Conway Road,<br />

Bethesda, MD 20817 (US). SANTIAGO,<br />

Francisco; 5308 Cedar Ridge Drive, Fredericksburg,<br />

VA 22407 (US). BOULAIS,<br />

Kevin, A.; 1315 Wilson Road, Waldorf, MD<br />

20602 (US).<br />

(74) BECHTEL, James, B.; NSWC- Dahlgren<br />

Division, Office of Patent Counsel, Code<br />

CD222, Building 183, Room 015, 17320<br />

Dahlgren Road, Dahlgren, VA 22448-5100<br />

(US).<br />

(84) EP (AT BE CH CY DE DK ES FI FR GB GR<br />

IE IT LU MC NL PT SE TR).<br />

(51) 7 H01L 21/8238, 21/336, 21/311<br />

(11) WO 01/84628<br />

(21) <strong>PCT</strong>/CA01/00639<br />

(13) A1<br />

(22) 3 May/mai <strong>2001</strong> (03.05.<strong>2001</strong>)<br />

(25) en (26) en<br />

(30) 0010650.0 4 May/mai 2000<br />

(04.05.2000)<br />

GB<br />

(43) 8 Nov/nov <strong>2001</strong> (08.11.<strong>2001</strong>)<br />

(54) METHOD OF FORMING SPACERS IN<br />

CMOS DEVICES<br />

REALISATION DE CALES D’ECARTE-<br />

MENT DANS DES CIRCUITS CMOS<br />

(71) MITEL CORPORATION [CA/CA]; 400<br />

March Road, Kanata, Ontario K2K 3H4<br />

(CA).<br />

(72) ROY, Marc; 85 Levis Street, Granby, Quebec<br />

J2N 2G2 (CA). DAIGLE, Manon; 11<br />

Principal Ouest, Farnham, Quebec J2N 1K4