TH ESE Mohamed H edi TOUATI TEST ET ... - Laboratoire TIMA

TH ESE Mohamed H edi TOUATI TEST ET ... - Laboratoire TIMA

TH ESE Mohamed H edi TOUATI TEST ET ... - Laboratoire TIMA

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

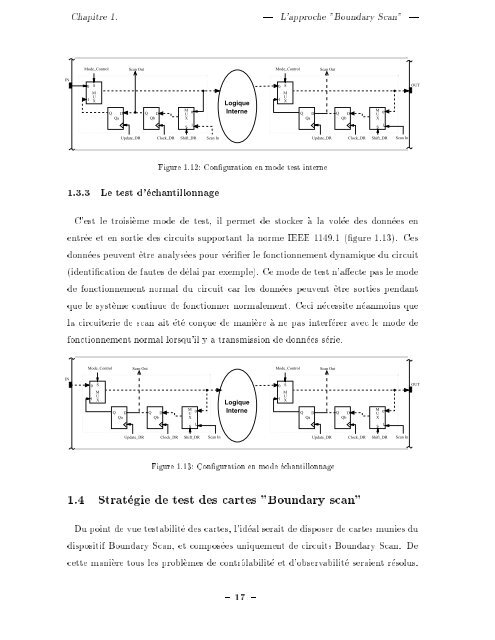

Chapitre 1. | L'approche "Boundary Scan" |<br />

Mode_Control<br />

Scan Out<br />

Mode_Control<br />

Scan Out<br />

IN<br />

0 S<br />

M<br />

UX<br />

1<br />

Q D<br />

Q D<br />

Qa<br />

Qb<br />

M<br />

UX<br />

0<br />

S<br />

1<br />

Logique<br />

Interne<br />

0<br />

1<br />

S<br />

M<br />

U<br />

X<br />

M<br />

Q D<br />

Q D<br />

U<br />

0<br />

Qa<br />

Qb<br />

X<br />

S<br />

1<br />

OUT<br />

Update_DR Clock_DR Shift_DR Scan In<br />

Update_DR Clock_DR Shift_DR<br />

Scan In<br />

Figure 1.12: Conguration en mode test interne<br />

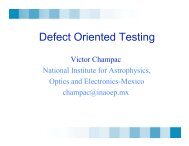

1.3.3 Le test d'echantillonnage<br />

C'est le troisieme mode de test, il permet de stocker a lavolee des donnees en<br />

entree et en sortie des circuits supportant la norme IEEE 1149.1 (gure 1.13). Ces<br />

donnees peuvent ^etre analysees pour verier le fonctionnement dynamique du circuit<br />

(identication de fautes de delai par exemple). Ce mode de test n'aecte pas le mode<br />

de fonctionnement normal du circuit car les donnees peuvent ^etre sorties pendant<br />

que le systeme continue de fonctionner normalement. Ceci necessite neanmoins que<br />

la circuiterie de scan ait ete concue de maniere a ne pas interferer avec le mode de<br />

fonctionnement normal lorsqu'il y a transmission de donnees serie.<br />

Mode_Control<br />

Scan Out<br />

Mode_Control<br />

Scan Out<br />

IN<br />

0 S<br />

M<br />

1 X U<br />

Q<br />

D<br />

Qa<br />

Q<br />

D<br />

Qb<br />

M<br />

U<br />

0<br />

X<br />

S<br />

1<br />

Logique<br />

Interne<br />

0 S<br />

M<br />

UX<br />

1<br />

Q D<br />

Qa<br />

Q<br />

D<br />

Qb<br />

M<br />

UX<br />

0<br />

S<br />

1<br />

OUT<br />

Update_DR Clock_DR Shift_DR Scan In<br />

Update_DR Clock_DR Shift_DR<br />

Scan In<br />

Figure 1.13: Conguration en mode echantillonnage<br />

1.4 Strategie de test des cartes "Boundary scan"<br />

Du point de vue testabilite des cartes, l'ideal serait de disposer de cartes munies du<br />

dispositif Boundary Scan, et composees uniquement de circuits Boundary Scan. De<br />

cette maniere tous les problemes de contr^olabilite et d'observabilite seraient resolus.<br />

{17 {