Single-Chip Low Cost Low Power RF-Transceiver (Rev. A)

Single-Chip Low Cost Low Power RF-Transceiver (Rev. A)

Single-Chip Low Cost Low Power RF-Transceiver (Rev. A)

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

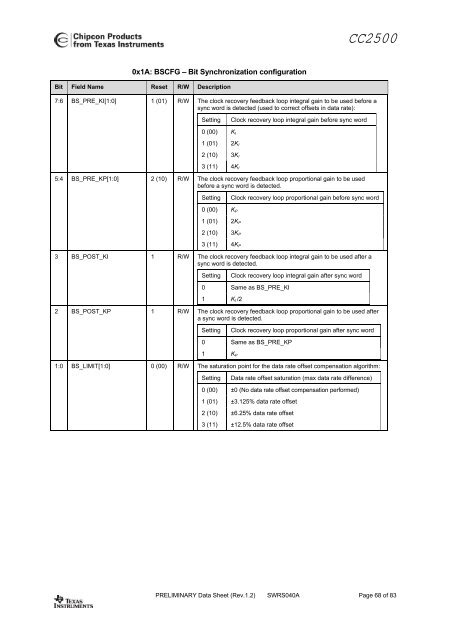

CC25000x1A: BSCFG – Bit Synchronization configurationBit Field Name Reset R/W Description7:6 BS_PRE_KI[1:0] 1 (01) R/W The clock recovery feedback loop integral gain to be used before async word is detected (used to correct offsets in data rate):SettingClock recovery loop integral gain before sync word0 (00) K I1 (01) 2K I2 (10) 3K I3 (11) 4K I5:4 BS_PRE_KP[1:0] 2 (10) R/W The clock recovery feedback loop proportional gain to be usedbefore a sync word is detected.SettingClock recovery loop proportional gain before sync word0 (00) K P1 (01) 2K P2 (10) 3K P3 (11) 4K P3 BS_POST_KI 1 R/W The clock recovery feedback loop integral gain to be used after async word is detected.SettingClock recovery loop integral gain after sync word0 Same as BS_PRE_KI1 K I /22 BS_POST_KP 1 R/W The clock recovery feedback loop proportional gain to be used aftera sync word is detected.SettingClock recovery loop proportional gain after sync word0 Same as BS_PRE_KP1 K P1:0 BS_LIMIT[1:0] 0 (00) R/W The saturation point for the data rate offset compensation algorithm:SettingData rate offset saturation (max data rate difference)0 (00) ±0 (No data rate offset compensation performed)1 (01) ±3.125% data rate offset2 (10) ±6.25% data rate offset3 (11) ±12.5% data rate offsetPRELIMINARY Data Sheet (<strong>Rev</strong>.1.2) SWRS040A Page 68 of 83

![td-res-4 [Compatibility Mode]](https://img.yumpu.com/45826987/1/184x260/td-res-4-compatibility-mode.jpg?quality=85)