Single-Chip Low Cost Low Power RF-Transceiver (Rev. A)

Single-Chip Low Cost Low Power RF-Transceiver (Rev. A)

Single-Chip Low Cost Low Power RF-Transceiver (Rev. A)

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

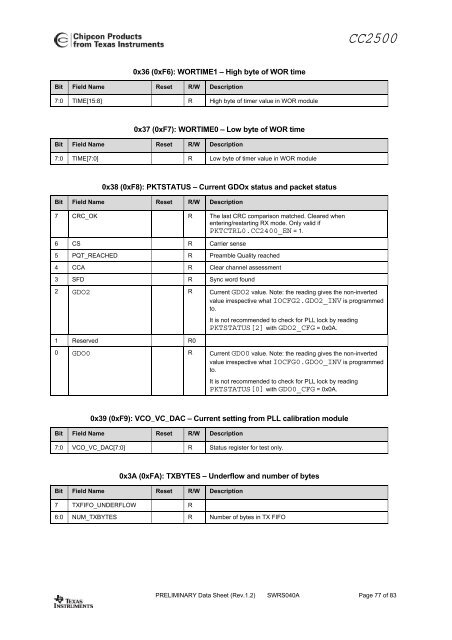

CC25000x36 (0xF6): WORTIME1 – High byte of WOR timeBit Field Name Reset R/W Description7:0 TIME[15:8] R High byte of timer value in WOR module0x37 (0xF7): WORTIME0 – <strong>Low</strong> byte of WOR timeBit Field Name Reset R/W Description7:0 TIME[7:0] R <strong>Low</strong> byte of timer value in WOR module0x38 (0xF8): PKTSTATUS – Current GDOx status and packet statusBit Field Name Reset R/W Description7 CRC_OK R The last CRC comparison matched. Cleared whenentering/restarting RX mode. Only valid ifPKTCTRL0.CC2400_EN = 1.6 CS R Carrier sense5 PQT_REACHED R Preamble Quality reached4 CCA R Clear channel assessment3 SFD R Sync word found2 GDO2 R Current GDO2 value. Note: the reading gives the non-invertedvalue irrespective what IOCFG2.GDO2_INV is programmedto.It is not recommended to check for PLL lock by readingPKTSTATUS[2] with GDO2_CFG = 0x0A.1 Reserved R00 GDO0 R Current GDO0 value. Note: the reading gives the non-invertedvalue irrespective what IOCFG0.GDO0_INV is programmedto.It is not recommended to check for PLL lock by readingPKTSTATUS[0] with GDO0_CFG = 0x0A.0x39 (0xF9): VCO_VC_DAC – Current setting from PLL calibration moduleBit Field Name Reset R/W Description7:0 VCO_VC_DAC[7:0] R Status register for test only.0x3A (0xFA): TXBYTES – Underflow and number of bytesBit Field Name Reset R/W Description7 TXFIFO_UNDE<strong>RF</strong>LOW R6:0 NUM_TXBYTES R Number of bytes in TX FIFOPRELIMINARY Data Sheet (<strong>Rev</strong>.1.2) SWRS040A Page 77 of 83

![td-res-4 [Compatibility Mode]](https://img.yumpu.com/45826987/1/184x260/td-res-4-compatibility-mode.jpg?quality=85)