TC1765_ds_v12 (TC1765_ds_v12_1202.pdf) - Infineon

TC1765_ds_v12 (TC1765_ds_v12_1202.pdf) - Infineon

TC1765_ds_v12 (TC1765_ds_v12_1202.pdf) - Infineon

- TAGS

- infineon

- www.infineon.com

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

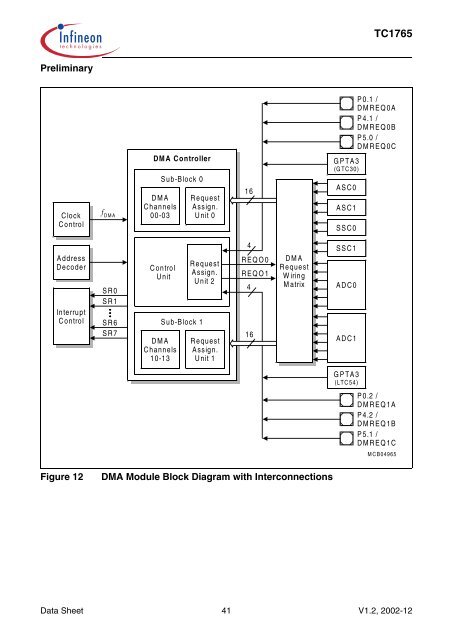

Preliminary<br />

Clock<br />

Control<br />

Address<br />

Decoder<br />

Interrupt<br />

Control<br />

f DMA<br />

SR0<br />

SR1<br />

SR6<br />

SR7<br />

DMA Controller<br />

DMA<br />

Channels<br />

00-03<br />

Control<br />

Unit<br />

DMA<br />

Channels<br />

10-13<br />

Sub-Block 0<br />

Sub-Block 1<br />

Request<br />

Assign.<br />

Unit 0<br />

Request<br />

Assign.<br />

Unit 2<br />

Request<br />

Assign.<br />

Unit 1<br />

Figure 12 DMA Module Block Diagram with Interconnections<br />

<strong>TC1765</strong><br />

MCB04965<br />

Data Sheet 41 V1.2, 2002-12<br />

16<br />

4<br />

REQO0<br />

REQO1<br />

4<br />

16<br />

DMA<br />

Request<br />

Wiring<br />

Matrix<br />

GPTA3<br />

(GTC30)<br />

ASC0<br />

ASC1<br />

SSC0<br />

SSC1<br />

ADC0<br />

ADC1<br />

GPTA3<br />

(LTC54)<br />

P0.1 /<br />

DMREQ0A<br />

P4.1 /<br />

DMREQ0B<br />

P5.0 /<br />

DMREQ0C<br />

P0.2 /<br />

DMREQ1A<br />

P4.2 /<br />

DMREQ1B<br />

P5.1 /<br />

DMREQ1C