TC1765_ds_v12 (TC1765_ds_v12_1202.pdf) - Infineon

TC1765_ds_v12 (TC1765_ds_v12_1202.pdf) - Infineon

TC1765_ds_v12 (TC1765_ds_v12_1202.pdf) - Infineon

- TAGS

- infineon

- www.infineon.com

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

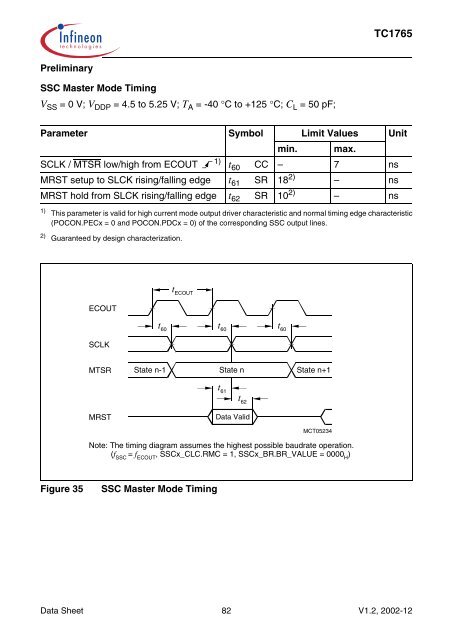

Preliminary<br />

SSC Master Mode Timing<br />

VSS = 0 V; VDDP = 4.5 to 5.25 V; TA = -40 °C to +125 °C; CL = 50 pF;<br />

Figure 35 SSC Master Mode Timing<br />

<strong>TC1765</strong><br />

Parameter Symbol Limit Values Unit<br />

min. max.<br />

SCLK / MTSR low/high from ECOUT<br />

1) t60 CC – 7 ns<br />

MRST setup to SLCK rising/falling edge t61 SR 18 2)<br />

– ns<br />

MRST hold from SLCK rising/falling edge t62 SR 10 2)<br />

– ns<br />

1) This parameter is valid for high current mode output driver characteristic and normal timing edge characteristic<br />

(POCON.PECx = 0 and POCON.PDCx = 0) of the corresponding SSC output lines.<br />

2) Guaranteed by design characterization.<br />

ECOUT<br />

SCLK<br />

MTSR<br />

MRST<br />

t 60<br />

t ECOUT<br />

t 60<br />

State n-1 State n<br />

State n+1<br />

t 61<br />

MCT05234<br />

Data Sheet 82 V1.2, 2002-12<br />

t 62<br />

Data Valid<br />

Note: The timing diagram assumes the highest possible baudrate operation.<br />

(f SSC = f ECOUT , SSCx_CLC.RMC = 1, SSCx_BR.BR_VALUE = 0000 H )<br />

t 60