TC1765_ds_v12 (TC1765_ds_v12_1202.pdf) - Infineon

TC1765_ds_v12 (TC1765_ds_v12_1202.pdf) - Infineon

TC1765_ds_v12 (TC1765_ds_v12_1202.pdf) - Infineon

- TAGS

- infineon

- www.infineon.com

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Preliminary<br />

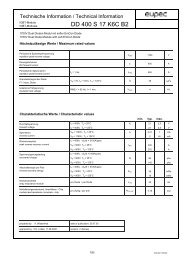

Input Clock Timing<br />

VDDOSC = 2.30 to 2.75 V; VSSOSC = 0 V; TA = -40 °C to +125 °C;<br />

Figure 27 Input Clock Timing<br />

<strong>TC1765</strong><br />

Parameter Symbol Limit Values Unit<br />

min. max.<br />

Oscillator clock frequency direct drive<br />

with PLL<br />

fOSC SR<br />

(= 1/tOSC) 4<br />

10<br />

16<br />

16<br />

MHz<br />

MHz<br />

Input clock frequency driving<br />

at XTAL1<br />

direct drive<br />

with PLL<br />

1/tOSCDD SR<br />

–<br />

10<br />

40<br />

30<br />

MHz<br />

MHz<br />

Input clock high time t1 SR 7 – ns<br />

Input clock low time t2 SR 7 – ns<br />

Input clock rise time t3 SR – 4 ns<br />

Input clock fall time t4 SR – 4 ns<br />

Input Clock<br />

at XTAL1<br />

0.5 V DDOSC<br />

t 1<br />

t OSC<br />

MCT04882<br />

Data Sheet 72 V1.2, 2002-12<br />

t 2<br />

t 4<br />

t 3<br />

V IHX<br />

V ILX