Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Prototyp <strong>eines</strong> digitalen EEGs auf Basis <strong>eines</strong> FPGAs<br />

für die Neurofeedbacksignalverarbeitung<br />

Wie in Abbildung 7 dargestellt, wer<strong>de</strong>n bei <strong>de</strong>r Datenübertragung<br />

zwischen FPGA und PC, die bei<strong>de</strong>n voneinan<strong>de</strong>r<br />

unabhängigen Endpunkte A und B <strong>de</strong>s USB-<br />

Schnittstellenbausteins FT2232 eingesetzt. Endpunkt<br />

A dient sowohl für die Übertragung von Steuerbefehlen<br />

an das FPGA, als auch <strong>de</strong>r vom FPGA generierten<br />

Status- und Fehlermeldungen an <strong>de</strong>n PC.<br />

<strong>Der</strong> Endpunkt B hingegen, wird ausschließlich für die<br />

Übertragung <strong>de</strong>r verarbeiteten EEG-Signale in Richtung<br />

<strong>de</strong>s PCs verwen<strong>de</strong>t. <strong>Der</strong> Empfang von Daten<br />

über <strong>de</strong>n Endpunkt B ist nicht vorgesehen.<br />

Die Kommunikation mit <strong>de</strong>m A/D-Umsetzer (ADC)<br />

erfolgt nach <strong>de</strong>m Master-Slave-Prinzip über <strong>de</strong>ssen<br />

SPI-Schnittstelle. Dabei fungiert das FPGA als Master,<br />

<strong>de</strong>r A/DUmsetzer als Slave. Insges<strong>am</strong>t sind vier<br />

Signalleitungen für die Anbindung <strong>de</strong>s A/D-Umsetzers<br />

an das FPGA erfor<strong>de</strong>rlich. Mit <strong>de</strong>m USB-Schnittstellenbaustein<br />

(USB) erfolgt die Kommunikation über<br />

<strong>de</strong>ssen „Fast Opto-Isolated Serial Interface“. Diese<br />

synchrone Schnittstelle benötigt lediglich vier Signalleitungen,<br />

was eine einfache galvanische Entkopplung<br />

dieser Schnittstelle ermöglicht. Die serielle Datenübertragung<br />

ist durch ein properitäres Protokoll realisiert,<br />

welches die Unterscheidungsmöglichkeit zwischen<br />

<strong>de</strong>n bei<strong>de</strong>n eigenständigen Endpunkten A und<br />

B berücksichtigt. Das FPGA stellt bei diesem properitären<br />

Protokoll in bei<strong>de</strong> Richtungen, die steuern<strong>de</strong><br />

Instanz <strong>de</strong>r Datenübertragung dar.<br />

Abbildung 7: Verwendung <strong>de</strong>r bei<strong>de</strong>n USB-Endpunkte<br />

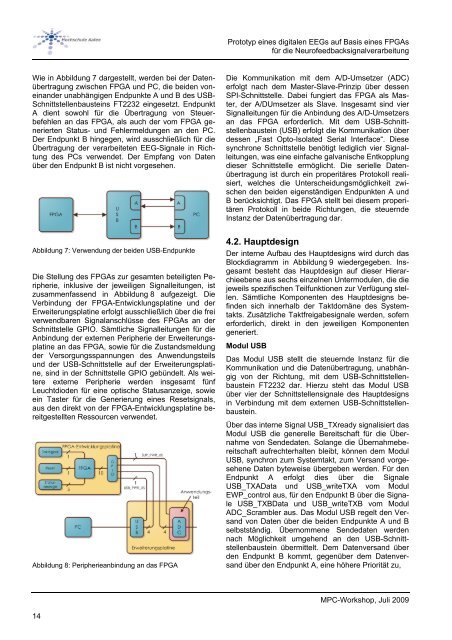

Die Stellung <strong>de</strong>s FPGAs zur ges<strong>am</strong>ten beteiligten Peripherie,<br />

inklusive <strong>de</strong>r jeweiligen Signalleitungen, ist<br />

zus<strong>am</strong>menfassend in Abbildung 8 aufgezeigt. Die<br />

Verbindung <strong>de</strong>r FPGA-Entwicklungsplatine und <strong>de</strong>r<br />

Erweiterungsplatine erfolgt ausschließlich über die frei<br />

verwendbaren Signalanschlüsse <strong>de</strong>s FPGAs an <strong>de</strong>r<br />

Schnittstelle GPIO. Sämtliche Signalleitungen für die<br />

Anbindung <strong>de</strong>r externen Peripherie <strong>de</strong>r Erweiterungsplatine<br />

an das FPGA, sowie für die Zustandsmeldung<br />

<strong>de</strong>r Versorgungsspannungen <strong>de</strong>s Anwendungsteils<br />

und <strong>de</strong>r USB-Schnittstelle auf <strong>de</strong>r Erweiterungsplatine,<br />

sind in <strong>de</strong>r Schnittstelle GPIO gebün<strong>de</strong>lt. Als weitere<br />

externe Peripherie wer<strong>de</strong>n insges<strong>am</strong>t fünf<br />

Leuchtdio<strong>de</strong>n für eine optische Statusanzeige, sowie<br />

ein Taster für die Generierung <strong>eines</strong> Resetsignals,<br />

aus <strong>de</strong>n direkt von <strong>de</strong>r FPGA-Entwicklungsplatine bereitgestellten<br />

Ressourcen verwen<strong>de</strong>t.<br />

Abbildung 8: Peripherieanbindung an das FPGA<br />

4.2. Haupt<strong>de</strong>sign<br />

<strong>Der</strong> interne Aufbau <strong>de</strong>s Haupt<strong>de</strong>signs wird durch das<br />

Blockdiagr<strong>am</strong>m in Abbildung 9 wie<strong>de</strong>rgegeben. Insges<strong>am</strong>t<br />

besteht das Haupt<strong>de</strong>sign auf dieser Hierarchieebene<br />

aus sechs einzelnen Untermodulen, die die<br />

jeweils spezifischen Teilfunktionen zur Verfügung stellen.<br />

Sämtliche Komponenten <strong>de</strong>s Haupt<strong>de</strong>signs befin<strong>de</strong>n<br />

sich innerhalb <strong>de</strong>r Taktdomäne <strong>de</strong>s Systemtakts.<br />

Zusätzliche Taktfreigabesignale wer<strong>de</strong>n, sofern<br />

erfor<strong>de</strong>rlich, direkt in <strong>de</strong>n jeweiligen Komponenten<br />

generiert.<br />

Modul USB<br />

Das Modul USB stellt die steuern<strong>de</strong> Instanz für die<br />

Kommunikation und die Datenübertragung, unabhängig<br />

von <strong>de</strong>r Richtung, mit <strong>de</strong>m USB-Schnittstellenbaustein<br />

FT2232 dar. Hierzu steht das Modul USB<br />

über vier <strong>de</strong>r Schnittstellensignale <strong>de</strong>s Haupt<strong>de</strong>signs<br />

in Verbindung mit <strong>de</strong>m externen USB-Schnittstellenbaustein.<br />

Über das interne Signal USB_TXready signalisiert das<br />

Modul USB die generelle Bereitschaft für die Übernahme<br />

von Sen<strong>de</strong>daten. Solange die Übernahmebereitschaft<br />

aufrechterhalten bleibt, können <strong>de</strong>m Modul<br />

USB, synchron zum Systemtakt, zum Versand vorgesehene<br />

Daten byteweise übergeben wer<strong>de</strong>n. Für <strong>de</strong>n<br />

Endpunkt A erfolgt dies über die Signale<br />

USB_TXAData und USB_writeTXA vom Modul<br />

EWP_control aus, für <strong>de</strong>n Endpunkt B über die Signale<br />

USB_TXBData und USB_writeTXB vom Modul<br />

ADC_Scr<strong>am</strong>bler aus. Das Modul USB regelt <strong>de</strong>n Versand<br />

von Daten über die bei<strong>de</strong>n Endpunkte A und B<br />

selbstständig. Übernommene Sen<strong>de</strong>daten wer<strong>de</strong>n<br />

nach Möglichkeit umgehend an <strong>de</strong>n USB-Schnittstellenbaustein<br />

übermittelt. Dem Datenversand über<br />

<strong>de</strong>n Endpunkt B kommt, gegenüber <strong>de</strong>m Datenversand<br />

über <strong>de</strong>n Endpunkt A, eine höhere Priorität zu,<br />

MPC-Workshop, Juli 2009<br />

14

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)