Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

„Entwurf <strong>eines</strong> High-Speed Multiplexers/Demultiplexers für einen Mischer in<br />

0,35µm Technologie“<br />

3. Allgem<strong>eines</strong><br />

3.1 Zur Simulation<br />

Für die einzelnen Blöcke wur<strong>de</strong>n zuerst Schaltbil<strong>de</strong>r<br />

(Schematics) mit <strong>de</strong>m Mentor IC Studio erstellt und<br />

dimensioniert. Für die anschließen<strong>de</strong> Simulation<br />

wur<strong>de</strong>n, mit Hilfe <strong>de</strong>r bereits bestehen<strong>de</strong>n Schaltung,<br />

die Eingangssignale durch Quellen dargestellt, um so<br />

die vorhan<strong>de</strong>ne Umgebung nachzubil<strong>de</strong>n. Für die<br />

Gatekapazitäten <strong>de</strong>r nachfolgen<strong>de</strong>n Transistoren und<br />

die Leitungskapazitäten sind entsprechend große<br />

Kapazitäten als Last an <strong>de</strong>n Ausgang <strong>de</strong>r Blöcke<br />

angeschlossen wor<strong>de</strong>n. Die Simulationen wur<strong>de</strong>n<br />

dann mit Än<strong>de</strong>rungen folgen<strong>de</strong>r Par<strong>am</strong>eter<br />

durchgeführt:<br />

4. Einzelne Blöcke<br />

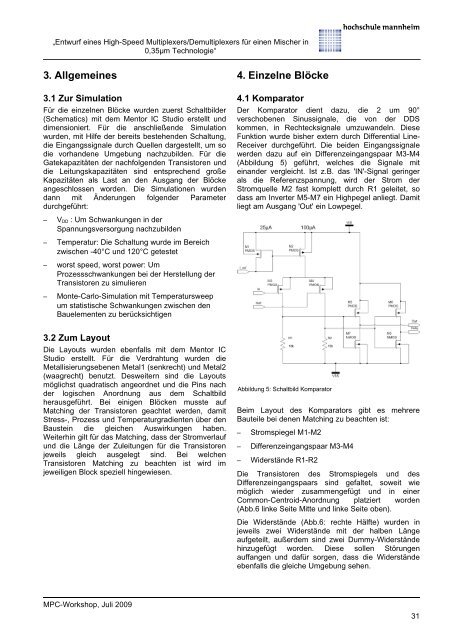

4.1 Komparator<br />

<strong>Der</strong> Komparator dient dazu, die 2 um 90°<br />

verschobenen Sinussignale, die von <strong>de</strong>r DDS<br />

kommen, in Rechtecksignale umzuwan<strong>de</strong>ln. Diese<br />

Funktion wur<strong>de</strong> bisher extern durch Differential Line-<br />

Receiver durchgeführt. Die bei<strong>de</strong>n Eingangssignale<br />

wer<strong>de</strong>n dazu auf ein Differenzeingangspaar M3-M4<br />

(Abbildung 5) geführt, welches die Signale mit<br />

einan<strong>de</strong>r vergleicht. Ist z.B. das 'IN'-Signal geringer<br />

als die Referenzspannung, wird <strong>de</strong>r Strom <strong>de</strong>r<br />

Stromquelle M2 fast komplett durch R1 geleitet, so<br />

dass <strong>am</strong> Inverter M5-M7 ein Highpegel anliegt. D<strong>am</strong>it<br />

liegt <strong>am</strong> Ausgang 'Out' ein Lowpegel.<br />

– V DD : Um Schwankungen in <strong>de</strong>r<br />

Spannungsversorgung nachzubil<strong>de</strong>n<br />

– Temperatur: Die Schaltung wur<strong>de</strong> im Bereich<br />

zwischen -40°C und 120°C getestet<br />

– worst speed, worst power: Um<br />

Prozessschwankungen bei <strong>de</strong>r Herstellung <strong>de</strong>r<br />

Transistoren zu simulieren<br />

– Monte-Carlo-Simulation mit Temperatursweep<br />

um statistische Schwankungen zwischen <strong>de</strong>n<br />

Bauelementen zu berücksichtigen<br />

3.2 Zum Layout<br />

Die Layouts wur<strong>de</strong>n ebenfalls mit <strong>de</strong>m Mentor IC<br />

Studio erstellt. Für die Verdrahtung wur<strong>de</strong>n die<br />

Metallisierungsebenen Metal1 (senkrecht) und Metal2<br />

(waagrecht) benutzt. Desweitern sind die Layouts<br />

möglichst quadratisch angeordnet und die Pins nach<br />

<strong>de</strong>r logischen Anordnung aus <strong>de</strong>m Schaltbild<br />

herausgeführt. Bei einigen Blöcken musste auf<br />

Matching <strong>de</strong>r Transistoren geachtet wer<strong>de</strong>n, d<strong>am</strong>it<br />

Stress-, Prozess und Temperaturgradienten über <strong>de</strong>n<br />

Baustein die gleichen Auswirkungen haben.<br />

Weiterhin gilt für das Matching, dass <strong>de</strong>r Stromverlauf<br />

und die Länge <strong>de</strong>r Zuleitungen für die Transistoren<br />

jeweils gleich ausgelegt sind. Bei welchen<br />

Transistoren Matching zu beachten ist wird im<br />

jeweiligen Block speziell hingewiesen.<br />

Abbildung 5: Schaltbild Komparator<br />

Beim Layout <strong>de</strong>s Komparators gibt es mehrere<br />

Bauteile bei <strong>de</strong>nen Matching zu beachten ist:<br />

– Stromspiegel M1-M2<br />

– Differenzeingangspaar M3-M4<br />

– Wi<strong>de</strong>rstän<strong>de</strong> R1-R2<br />

Die Transistoren <strong>de</strong>s Stromspiegels und <strong>de</strong>s<br />

Differenzeingangspaars sind gefaltet, soweit wie<br />

möglich wie<strong>de</strong>r zus<strong>am</strong>mengefügt und in einer<br />

Common-Centroid-Anordnung platziert wor<strong>de</strong>n<br />

(Abb.6 linke Seite Mitte und linke Seite oben).<br />

Die Wi<strong>de</strong>rstän<strong>de</strong> (Abb.6: rechte Hälfte) wur<strong>de</strong>n in<br />

jeweils zwei Wi<strong>de</strong>rstän<strong>de</strong> mit <strong>de</strong>r halben Länge<br />

aufgeteilt, außer<strong>de</strong>m sind zwei Dummy-Wi<strong>de</strong>rstän<strong>de</strong><br />

hinzugefügt wor<strong>de</strong>n. Diese sollen Störungen<br />

auffangen und dafür sorgen, dass die Wi<strong>de</strong>rstän<strong>de</strong><br />

ebenfalls die gleiche Umgebung sehen.<br />

MPC-Workshop, Juli 2009<br />

31

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)