Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

<strong>Der</strong> <strong>UMC</strong> <strong>0.18</strong> <strong>Design</strong> <strong>Flow</strong> <strong>am</strong> <strong>Beispiel</strong> <strong>eines</strong> <strong>PDA</strong>-Prozessor ICs<br />

Tab.1: Flächenvergleich <strong>de</strong>r Technologien<br />

Zelle<br />

Memory<br />

2 Input<br />

AND<br />

2 Input<br />

MUX<br />

2 Input<br />

NOR<br />

<strong>UMC</strong> <strong>0.18</strong><br />

[µm]<br />

8kWord:<br />

563x1391<br />

3. Entwurfsablauf<br />

AMIS 0.35<br />

[µm]<br />

8kByte:<br />

1366x1960<br />

<strong>Der</strong> in Abbildung 3 dargestellte <strong>Design</strong> <strong>Flow</strong> zeigt<br />

welche Progr<strong>am</strong>me zum Einsatz kommen und welche<br />

Dateien für die einzelnen Progr<strong>am</strong>me benötigt wer<strong>de</strong>n.<br />

Für das eingesetzte Mikrocontrollersystem SIRIUS<br />

existiert ein SIRIUS-<strong>Design</strong>-Kit, welcher verschie<strong>de</strong>ne<br />

Softwaretools zur Verfügung stellt. Unter an<strong>de</strong>rem<br />

eine Entwicklungsumgebung, welche es ermöglicht<br />

einen C-Co<strong>de</strong> in ein Hex-File zu compilieren und es<br />

mit in die VHDL-Simulation miteinzubin<strong>de</strong>n.<br />

3.1 Synthese auf Zieltechnologie<br />

Faktor<br />

6,8<br />

2,48x5,04 6x12 5,76<br />

4,34x5,04 10,5x12 5,76<br />

1,86x5,04 4,5x12 5,76<br />

2 Input OR 2,48x5.04 6x12 5,76<br />

D Flip-Flop 10,54x5,04 21x12 4,74<br />

IO Input<br />

Buffer<br />

62,6x140,1 144x183 3<br />

Für die Synthese mit <strong>Design</strong> Vision von Synopsys<br />

wer<strong>de</strong>n die Technologiebeschreibung <strong>de</strong>r Logikgatter<br />

verwen<strong>de</strong>t. Die im <strong>UMC</strong> <strong>Design</strong> Kit enthaltene Dateien<br />

sind sowohl als ASCI Datei im “.lib“-Format als auch in<br />

compilierter Form im synopsysspezifischen “*.db*-<br />

Format vorhan<strong>de</strong>n. Die daraus resultieren<strong>de</strong> Netzliste<br />

wird im Verilog-Format für das nachfolgen<strong>de</strong> Layout<br />

Progr<strong>am</strong>m Encounter herausgeschrieben und als<br />

generische VHDL-Netzliste, welche sich lediglich in<br />

<strong>de</strong>r N<strong>am</strong>ensgebung <strong>de</strong>r Standardzellen unterschei<strong>de</strong>t.<br />

Ausgehend von <strong>de</strong>n <strong>UMC</strong>-Standardzellen sind unter<br />

Ausschluß von speziellen Zellen die Grundfunktionen<br />

<strong>de</strong>r Digitaltechnik wie AND, OR, XOR, NOR, MUX,<br />

INV und D-FlipFlop nachprogr<strong>am</strong>miert. Mithilfe dieser<br />

Grundzellen und <strong>de</strong>r generischen Netzliste ist eine<br />

Umsetzung in je<strong>de</strong> beliebige Zieltechnolgie<br />

realisierbar. <strong>Der</strong> ASIC-Entwickler hat dadurch die<br />

Möglichkeit, die digitale Zellen seiner Schaltung mit<br />

geringsten strukturellen Abweichungen auf einem<br />

FPGA zu verifizieren.<br />

3.2 Von <strong>de</strong>r Netzliste zum Chiplayout<br />

Die Verilog-Netzliste, welche man aus <strong>de</strong>r Synthese<br />

erhält, kann direkt zum Routen über das CAE-Tool<br />

Encounter <strong>de</strong>r Firma Ca<strong>de</strong>nce eingelesen wer<strong>de</strong>n.<br />

Das Tool ist im platzieren <strong>de</strong>r in <strong>de</strong>r Netzliste<br />

verankerten Zellen, routen, erneute Taktsynthese,<br />

Clock-Tree-Analyse und layouten komfortabel zu<br />

bedienen. Durch einen ausgereiften Platzier- und<br />

Routingalgorithmus können dicht geroutete <strong>Design</strong><br />

erzielt wer<strong>de</strong>n, um möglichst keine teuere<br />

Siliziumfläche zu verschwen<strong>de</strong>n. Nach <strong>de</strong>m<br />

Platzieren, <strong>de</strong>r Taktsynthese und <strong>de</strong>m Been<strong>de</strong>n <strong>de</strong>s<br />

Routens lässt man sich die um Buffer- und<br />

Inverterzellen erweiterte timing-optimierte Netzliste<br />

herausschreiben. Mit <strong>de</strong>m zusätzlich generierten SDF-<br />

File (Standard Delay Format) lässt sich unter realen<br />

Verzögerungszeiten <strong>de</strong>r digitale Schaltungspart <strong>de</strong>s<br />

<strong>Design</strong>s erneut simulieren. Für analoge Schaltungsentwicklung<br />

ist das Layout-Tool Encounter nicht<br />

geeignet.<br />

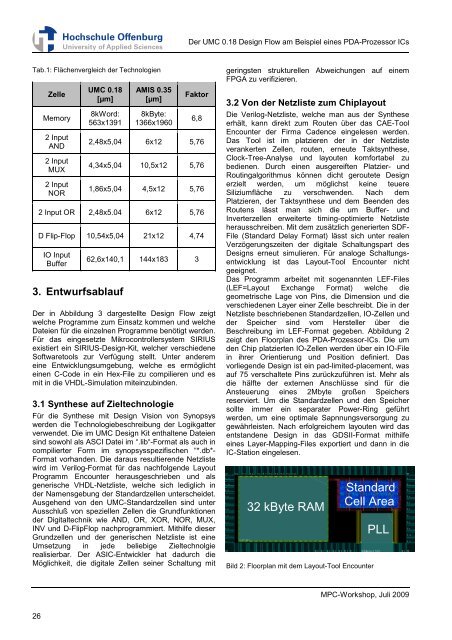

Das Progr<strong>am</strong>m arbeitet mit sogenannten LEF-Files<br />

(LEF=Layout Exchange Format) welche die<br />

geometrische Lage von Pins, die Dimension und die<br />

verschie<strong>de</strong>nen Layer einer Zelle beschreibt. Die in <strong>de</strong>r<br />

Netzliste beschriebenen Standardzellen, IO-Zellen und<br />

<strong>de</strong>r Speicher sind vom Hersteller über die<br />

Beschreibung im LEF-Format gegeben. Abbildung 2<br />

zeigt <strong>de</strong>n Floorplan <strong>de</strong>s <strong>PDA</strong>-Prozessor-ICs. Die um<br />

<strong>de</strong>n Chip platzierten IO-Zellen wer<strong>de</strong>n über ein IO-File<br />

in ihrer Orientierung und Position <strong>de</strong>finiert. Das<br />

vorliegen<strong>de</strong> <strong>Design</strong> ist ein pad-limited-placement, was<br />

auf 75 verschaltete Pins zurückzuführen ist. Mehr als<br />

die hälfte <strong>de</strong>r externen Anschlüsse sind für die<br />

Ansteuerung <strong>eines</strong> 2Mbyte großen Speichers<br />

reserviert. Um die Standardzellen und <strong>de</strong>n Speicher<br />

sollte immer ein separater Power-Ring geführt<br />

wer<strong>de</strong>n, um eine optimale Sapnnungsversorgung zu<br />

gewährleisten. Nach erfolgreichem layouten wird das<br />

entstan<strong>de</strong>ne <strong>Design</strong> in das GDSII-Format mithilfe<br />

<strong>eines</strong> Layer-Mapping-Files exportiert und dann in die<br />

IC-Station eingelesen.<br />

32 kByte RAM<br />

Standard<br />

Cell Area<br />

Bild 2: Floorplan mit <strong>de</strong>m Layout-Tool Encounter<br />

PLL<br />

MPC-Workshop, Juli 2009<br />

26

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)