Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Dimensionierung und Entwurfszentrierung analoger Schaltungen mit WiCkeD<br />

Tab. 5: Symmetrieüberlegungen für <strong>de</strong>n OPV<br />

Gleiches<br />

Transistoren<br />

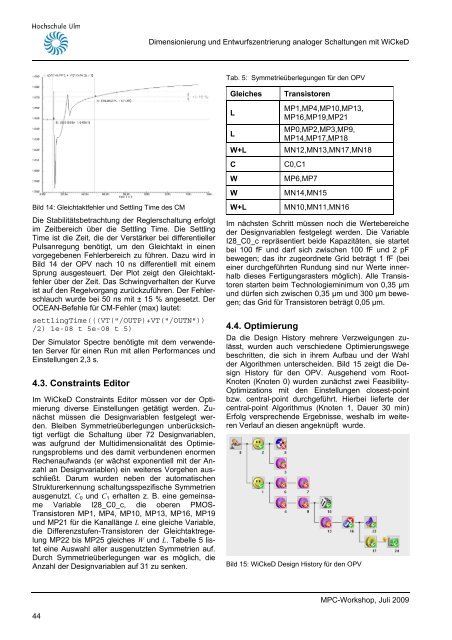

Bild 14: Gleichtaktfehler und Settling Time <strong>de</strong>s CM<br />

Die Stabilitätsbetrachtung <strong>de</strong>r Reglerschaltung erfolgt<br />

im Zeitbereich über die Settling Time. Die Settling<br />

Time ist die Zeit, die <strong>de</strong>r Verstärker bei differentieller<br />

Pulsanregung benötigt, um <strong>de</strong>n Gleichtakt in einen<br />

vorgegebenen Fehlerbereich zu führen. Dazu wird in<br />

Bild 14 <strong>de</strong>r OPV nach 10 ns differentiell mit einem<br />

Sprung ausgesteuert. <strong>Der</strong> Plot zeigt <strong>de</strong>n Gleichtaktfehler<br />

über <strong>de</strong>r Zeit. Das Schwingverhalten <strong>de</strong>r Kurve<br />

ist auf <strong>de</strong>n Regelvorgang zurückzuführen. <strong>Der</strong> Fehlerschlauch<br />

wur<strong>de</strong> bei 50 ns mit ± 15 % angesetzt. <strong>Der</strong><br />

OCEAN-Befehle für CM-Fehler (max) lautet:<br />

settlingTime(((VT("/OUTP)+VT("/OUTN"))<br />

/2) 1e-08 t 5e-08 t 5)<br />

<strong>Der</strong> Simulator Spectre benötigte mit <strong>de</strong>m verwen<strong>de</strong>ten<br />

Server für einen Run mit allen Performances und<br />

Einstellungen 2,3 s.<br />

4.3. Constraints Editor<br />

Im WiCkeD Constraints Editor müssen vor <strong>de</strong>r Optimierung<br />

diverse Einstellungen getätigt wer<strong>de</strong>n. Zunächst<br />

müssen die <strong>Design</strong>variablen festgelegt wer<strong>de</strong>n.<br />

Bleiben Symmetrieüberlegungen unberücksichtigt<br />

verfügt die Schaltung über 72 <strong>Design</strong>variablen,<br />

was aufgrund <strong>de</strong>r Multidimensionalität <strong>de</strong>s Optimierungsproblems<br />

und <strong>de</strong>s d<strong>am</strong>it verbun<strong>de</strong>nen enormen<br />

Rechenaufwands (er wächst exponentiell mit <strong>de</strong>r Anzahl<br />

an <strong>Design</strong>variablen) ein weiteres Vorgehen ausschließt.<br />

Darum wur<strong>de</strong>n neben <strong>de</strong>r automatischen<br />

Strukturerkennung schaltungsspezifische Symmetrien<br />

ausgenutzt. C 0 und C 1 erhalten z. B. eine gemeins<strong>am</strong>e<br />

Variable I28_C0_c, die oberen PMOS-<br />

Transistoren MP1, MP4, MP10, MP13, MP16, MP19<br />

und MP21 für die Kanallänge L eine gleiche Variable,<br />

die Differenzstufen-Transistoren <strong>de</strong>r Gleichtaktregelung<br />

MP22 bis MP25 gleiches W und L. Tabelle 5 listet<br />

eine Auswahl aller ausgenutzten Symmetrien auf.<br />

Durch Symmetrieüberlegungen war es möglich, die<br />

Anzahl <strong>de</strong>r <strong>Design</strong>variablen auf 31 zu senken.<br />

L<br />

L<br />

W+L<br />

C<br />

W<br />

W<br />

W+L<br />

MP1,MP4,MP10,MP13,<br />

MP16,MP19,MP21<br />

MP0,MP2,MP3,MP9,<br />

MP14,MP17,MP18<br />

MN12,MN13,MN17,MN18<br />

C0,C1<br />

MP6,MP7<br />

MN14,MN15<br />

MN10,MN11,MN16<br />

Im nächsten Schritt müssen noch die Wertebereiche<br />

<strong>de</strong>r <strong>Design</strong>variablen festgelegt wer<strong>de</strong>n. Die Variable<br />

I28_C0_c repräsentiert bei<strong>de</strong> Kapazitäten, sie startet<br />

bei 100 fF und darf sich zwischen 100 fF und 2 pF<br />

bewegen; das ihr zugeordnete Grid beträgt 1 fF (bei<br />

einer durchgeführten Rundung sind nur Werte innerhalb<br />

dieses Fertigungsrasters möglich). Alle Transistoren<br />

starten beim Technologieminimum von 0,35 µm<br />

und dürfen sich zwischen 0,35 µm und 300 µm bewegen;<br />

das Grid für Transistoren beträgt 0,05 µm.<br />

4.4. Optimierung<br />

Da die <strong>Design</strong> History mehrere Verzweigungen zulässt,<br />

wur<strong>de</strong>n auch verschie<strong>de</strong>ne Optimierungswege<br />

beschritten, die sich in ihrem Aufbau und <strong>de</strong>r Wahl<br />

<strong>de</strong>r Algorithmen unterschei<strong>de</strong>n. Bild 15 zeigt die <strong>Design</strong><br />

History für <strong>de</strong>n OPV. Ausgehend vom Root-<br />

Knoten (Knoten 0) wur<strong>de</strong>n zunächst zwei Feasibility-<br />

Optimizations mit <strong>de</strong>n Einstellungen closest-point<br />

bzw. central-point durchgeführt. Hierbei lieferte <strong>de</strong>r<br />

central-point Algorithmus (Knoten 1, Dauer 30 min)<br />

Erfolg versprechen<strong>de</strong> Ergebnisse, weshalb im weiteren<br />

Verlauf an diesen angeknüpft wur<strong>de</strong>.<br />

Bild 15: WiCkeD <strong>Design</strong> History für <strong>de</strong>n OPV<br />

MPC-Workshop, Juli 2009<br />

44

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)