Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Cache-Speicher für <strong>de</strong>n Softprozessor SIRIUS mit DDR-Interface<br />

• 32 MB DDR-RAM<br />

• USB-Blaster zum Progr<strong>am</strong>mieren <strong>de</strong>s FPGAs<br />

• 50 MHz Oszillator<br />

• Jeweils 4 Taster und LEDs<br />

• HSMC-Anschlussleiste für Zusatzplatinen<br />

5.1. DDR-RAM<br />

Bei DDR-RAMs han<strong>de</strong>lt es sich um dyn<strong>am</strong>ische Speicher<br />

mit großen Kapazitäten, sogenannte DRAMs. Um<br />

diese Kapazitäten auf kleinen Raum zu erhalten, wer<strong>de</strong>n<br />

die Datenbit mit Kon<strong>de</strong>nsatoren gespeichert. Da<br />

sich die Kon<strong>de</strong>nsatoren jedoch über unerwünschte<br />

Leckströme entla<strong>de</strong>n, geht <strong>de</strong>r Speicherinhalt nach<br />

kurzer Zeit verloren. Aus diesem Grund müssen die<br />

Daten im Speicher zyklisch mit einem sogenannten<br />

„Refresh“ aktualisiert wer<strong>de</strong>n. Im DRAM sind die<br />

Speicherzellen zeilenweise angeordnet.<br />

Um Adressleitungen zu sparen, wird beim Zugriff über<br />

die gleichen Leitungen zuerst die Zeilenadresse und<br />

dann die Wortadresse mit <strong>de</strong>nselben Leitungen übertragen.<br />

Durch <strong>de</strong>n internen Aufbau dauert <strong>de</strong>r Zugriff<br />

auf DRAMs <strong>de</strong>utlich länger als auf statische RAMs,<br />

jedoch können die zus<strong>am</strong>menhängen<strong>de</strong>n Daten<br />

innerhalb einer Zeile als “Burst“ ausgelesen wer<strong>de</strong>n.<br />

Dabei wer<strong>de</strong>n nach <strong>de</strong>r relativ langen Zugriffszeit für<br />

die erste Speicherzelle die folgen<strong>de</strong>n mit je<strong>de</strong>m<br />

Taktzyklus gelesen bzw. geschrieben.<br />

167 MHz * 16 Bit *2 = 637 MB/s<br />

Durch <strong>de</strong>n zyklischen Refresh und vor allem <strong>de</strong>n<br />

hohen Zugriffszeiten wer<strong>de</strong>n in <strong>de</strong>r Praxis jedoch nur<br />

Datenraten erreicht, die bei etwa 50% dieser Angaben<br />

liegen. Die Speichergröße <strong>de</strong>s verwen<strong>de</strong>ten DDR-<br />

RAMs ist mit 32 MB auch für zukünftige<br />

Anfor<strong>de</strong>rungen ausreichend.<br />

5.2. Weitere Hardware-Komponenten<br />

Da das Mikrocontrollersystem in <strong>de</strong>r bisherigen<br />

Version <strong>de</strong>n Flash-Speicher M25P40 <strong>de</strong>r Firma ST<br />

zum Booten <strong>de</strong>s Systems benötigt, soll dieser an das<br />

System angeschlossen wer<strong>de</strong>n. Dazu wird eine<br />

Zusatzplatine <strong>de</strong>r Firma Bitec verwen<strong>de</strong>t, die über die<br />

HSMC-Anschlussleiste mit <strong>de</strong>m Entwicklungsboard<br />

verbun<strong>de</strong>n wird. 158 Anschlüsse <strong>de</strong>s FPGAs sind<br />

direkt auf <strong>de</strong>m Board verfügbar, sowie Versorgungsspannungen<br />

von 3,3 und 12 Volt. Abbildung 5.3 zeigt<br />

Vor<strong>de</strong>r- und Rückseite <strong>de</strong>r Zusatzplatine.<br />

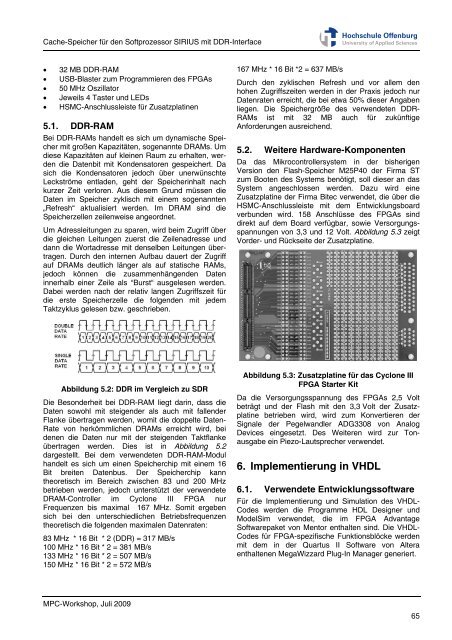

Abbildung 5.2: DDR im Vergleich zu SDR<br />

Die Beson<strong>de</strong>rheit bei DDR-RAM liegt darin, dass die<br />

Daten sowohl mit steigen<strong>de</strong>r als auch mit fallen<strong>de</strong>r<br />

Flanke übertragen wer<strong>de</strong>n, womit die doppelte Daten-<br />

Rate von herkömmlichen DRAMs erreicht wird, bei<br />

<strong>de</strong>nen die Daten nur mit <strong>de</strong>r steigen<strong>de</strong>n Taktflanke<br />

übertragen wer<strong>de</strong>n. Dies ist in Abbildung 5.2<br />

dargestellt. Bei <strong>de</strong>m verwen<strong>de</strong>ten DDR-RAM-Modul<br />

han<strong>de</strong>lt es sich um einen Speicherchip mit einem 16<br />

Bit breiten Datenbus. <strong>Der</strong> Speicherchip kann<br />

theoretisch im Bereich zwischen 83 und 200 MHz<br />

betrieben wer<strong>de</strong>n, jedoch unterstützt <strong>de</strong>r verwen<strong>de</strong>te<br />

DRAM-Controller im Cyclone III FPGA nur<br />

Frequenzen bis maximal 167 MHz. Somit ergeben<br />

sich bei <strong>de</strong>n unterschiedlichen Betriebsfrequenzen<br />

theoretisch die folgen<strong>de</strong>n maximalen Datenraten:<br />

83 MHz * 16 Bit * 2 (DDR) = 317 MB/s<br />

100 MHz * 16 Bit * 2 = 381 MB/s<br />

133 MHz * 16 Bit * 2 = 507 MB/s<br />

150 MHz * 16 Bit * 2 = 572 MB/s<br />

Abbildung 5.3: Zusatzplatine für das Cyclone III<br />

FPGA Starter Kit<br />

Da die Versorgungsspannung <strong>de</strong>s FPGAs 2,5 Volt<br />

beträgt und <strong>de</strong>r Flash mit <strong>de</strong>n 3,3 Volt <strong>de</strong>r Zusatzplatine<br />

betrieben wird, wird zum Konvertieren <strong>de</strong>r<br />

Signale <strong>de</strong>r Pegelwandler ADG3308 von Analog<br />

Devices eingesetzt. Des Weiteren wird zur Tonausgabe<br />

ein Piezo-Lautsprecher verwen<strong>de</strong>t.<br />

6. Implementierung in VHDL<br />

6.1. Verwen<strong>de</strong>te Entwicklungssoftware<br />

Für die Implementierung und Simulation <strong>de</strong>s VHDL-<br />

Co<strong>de</strong>s wer<strong>de</strong>n die Progr<strong>am</strong>me HDL <strong>Design</strong>er und<br />

Mo<strong>de</strong>lSim verwen<strong>de</strong>t, die im FPGA Advantage<br />

Softwarepaket von Mentor enthalten sind. Die VHDL-<br />

Co<strong>de</strong>s für FPGA-spezifische Funktionsblöcke wer<strong>de</strong>n<br />

mit <strong>de</strong>m in <strong>de</strong>r Quartus II Software von Altera<br />

enthaltenen MegaWizzard Plug-In Manager generiert.<br />

MPC-Workshop, Juli 2009<br />

65

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)