Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Neues von <strong>de</strong>r DATE 2009<br />

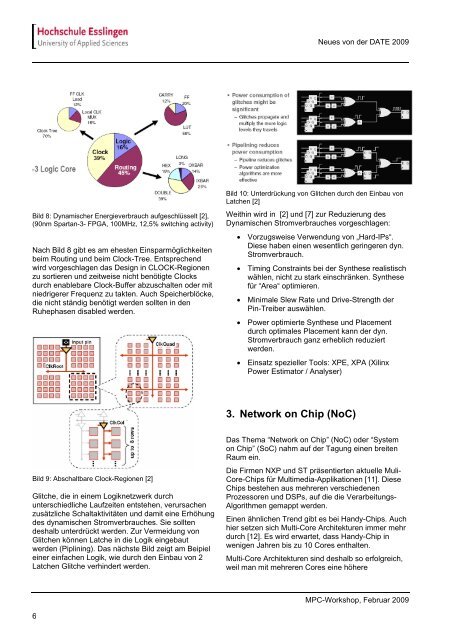

Bild 8: Dyn<strong>am</strong>ischer Energieverbrauch aufgeschlüsselt [2],<br />

(90nm Spartan-3- FPGA, 100MHz, 12,5% switching activity)<br />

Nach Bild 8 gibt es <strong>am</strong> ehesten Einsparmöglichkeiten<br />

beim Routing und beim Clock-Tree. Entsprechend<br />

wird vorgeschlagen das <strong>Design</strong> in CLOCK-Regionen<br />

zu sortieren und zeitweise nicht benötigte Clocks<br />

durch enablebare Clock-Buffer abzuschalten o<strong>de</strong>r mit<br />

niedrigerer Frequenz zu takten. Auch Speicherblöcke,<br />

die nicht ständig benötigt wer<strong>de</strong>n sollten in <strong>de</strong>n<br />

Ruhephasen disabled wer<strong>de</strong>n.<br />

Bild 10: Unterdrückung von Glitchen durch <strong>de</strong>n Einbau von<br />

Latchen [2]<br />

Weithin wird in [2] und [7] zur Reduzierung <strong>de</strong>s<br />

Dyn<strong>am</strong>ischen Stromverbrauches vorgeschlagen:<br />

• Vorzugsweise Verwendung von „Hard-IPs“.<br />

Diese haben einen wesentlich geringeren dyn.<br />

Stromverbrauch.<br />

• Timing Constraints bei <strong>de</strong>r Synthese realistisch<br />

wählen, nicht zu stark einschränken. Synthese<br />

für “Area“ optimieren.<br />

• Minimale Slew Rate und Drive-Strength <strong>de</strong>r<br />

Pin-Treiber auswählen.<br />

• Power optimierte Synthese und Placement<br />

durch optimales Placement kann <strong>de</strong>r dyn.<br />

Stromverbrauch ganz erheblich reduziert<br />

wer<strong>de</strong>n.<br />

• Einsatz spezieller Tools: XPE, XPA (Xilinx<br />

Power Estimator / Analyser)<br />

3. Network on Chip (NoC)<br />

Bild 9: Abschaltbare Clock-Regionen [2]<br />

Glitche, die in einem Logiknetzwerk durch<br />

unterschiedliche Laufzeiten entstehen, verursachen<br />

zusätzliche Schaltaktivitäten und d<strong>am</strong>it eine Erhöhung<br />

<strong>de</strong>s dyn<strong>am</strong>ischen Stromverbrauches. Sie sollten<br />

<strong>de</strong>shalb unterdrückt wer<strong>de</strong>n. Zur Vermeidung von<br />

Glitchen können Latche in die Logik eingebaut<br />

wer<strong>de</strong>n (Piplining). Das nächste Bild zeigt <strong>am</strong> Beipiel<br />

einer einfachen Logik, wie durch <strong>de</strong>n Einbau von 2<br />

Latchen Glitche verhin<strong>de</strong>rt wer<strong>de</strong>n.<br />

Das Thema “Network on Chip” (NoC) o<strong>de</strong>r “System<br />

on Chip” (SoC) nahm auf <strong>de</strong>r Tagung einen breiten<br />

Raum ein.<br />

Die Firmen NXP und ST präsentierten aktuelle Muli-<br />

Core-Chips für Multimedia-Applikationen [11]. Diese<br />

Chips bestehen aus mehreren verschie<strong>de</strong>nen<br />

Prozessoren und DSPs, auf die die Verarbeitungs-<br />

Algorithmen gemappt wer<strong>de</strong>n.<br />

Einen ähnlichen Trend gibt es bei Handy-Chips. Auch<br />

hier setzen sich Multi-Core Architekturen immer mehr<br />

durch [12]. Es wird erwartet, dass Handy-Chip in<br />

wenigen Jahren bis zu 10 Cores enthalten.<br />

Multi-Core Architekturen sind <strong>de</strong>shalb so erfolgreich,<br />

weil man mit mehreren Cores eine höhere<br />

MPC-Workshop, Februar 2009<br />

6

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)