Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Vom UML-Mo<strong>de</strong>ll einer Zustandsmaschine zu <strong>de</strong>ren<br />

VHDL- und SystemC-Architektur<br />

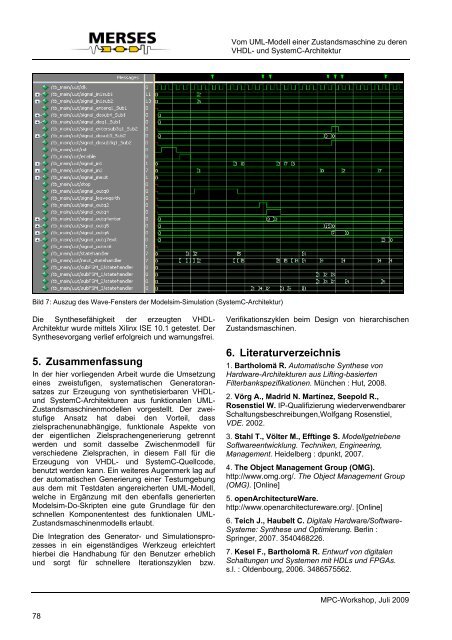

Bild 7: Auszug <strong>de</strong>s Wave-Fensters <strong>de</strong>r Mo<strong>de</strong>lsim-Simulation (SystemC-Architektur)<br />

Die Synthesefähigkeit <strong>de</strong>r erzeugten VHDL-<br />

Architektur wur<strong>de</strong> mittels Xilinx ISE 10.1 getestet. <strong>Der</strong><br />

Synthesevorgang verlief erfolgreich und warnungsfrei.<br />

5. Zus<strong>am</strong>menfassung<br />

In <strong>de</strong>r hier vorliegen<strong>de</strong>n Arbeit wur<strong>de</strong> die Umsetzung<br />

<strong>eines</strong> zweistufigen, systematischen Generatoransatzes<br />

zur Erzeugung von synthetisierbaren VHDLund<br />

SystemC-Architekturen aus funktionalen UML-<br />

Zustandsmaschinenmo<strong>de</strong>llen vorgestellt. <strong>Der</strong> zweistufige<br />

Ansatz hat dabei <strong>de</strong>n Vorteil, dass<br />

zielsprachenunabhängige, funktionale Aspekte von<br />

<strong>de</strong>r eigentlichen Zielsprachengenerierung getrennt<br />

wer<strong>de</strong>n und somit dasselbe Zwischenmo<strong>de</strong>ll für<br />

verschie<strong>de</strong>ne Zielsprachen, in diesem Fall für die<br />

Erzeugung von VHDL- und SystemC-Quellco<strong>de</strong>,<br />

benutzt wer<strong>de</strong>n kann. Ein weiteres Augenmerk lag auf<br />

<strong>de</strong>r automatischen Generierung einer Testumgebung<br />

aus <strong>de</strong>m mit Testdaten angereicherten UML-Mo<strong>de</strong>ll,<br />

welche in Ergänzung mit <strong>de</strong>n ebenfalls generierten<br />

Mo<strong>de</strong>lsim-Do-Skripten eine gute Grundlage für <strong>de</strong>n<br />

schnellen Komponententest <strong>de</strong>s funktionalen UML-<br />

Zustandsmaschinenmo<strong>de</strong>lls erlaubt.<br />

Die Integration <strong>de</strong>s Generator- und Simulationsprozesses<br />

in ein eigenständiges Werkzeug erleichtert<br />

hierbei die Handhabung für <strong>de</strong>n Benutzer erheblich<br />

und sorgt für schnellere Iterationszyklen bzw.<br />

Verifikationszyklen beim <strong>Design</strong> von hierarchischen<br />

Zustandsmaschinen.<br />

6. Literaturverzeichnis<br />

1. Bartholomä R. Automatische Synthese von<br />

Hardware-Architekturen aus Lifting-basierten<br />

Filterbankspezifikationen. München : Hut, 2008.<br />

2. Vörg A., Madrid N. Martínez, Seepold R.,<br />

Rosenstiel W. IP-Qualifizierung wie<strong>de</strong>rverwendbarer<br />

Schaltungsbeschreibungen,Wolfgang Rosenstiel,<br />

VDE. 2002.<br />

3. Stahl T., Völter M., Efftinge S. Mo<strong>de</strong>llgetriebene<br />

Softwareentwicklung. Techniken, Engineering,<br />

Management. Hei<strong>de</strong>lberg : dpunkt, 2007.<br />

4. The Object Management Group (OMG).<br />

http://www.omg.org/. The Object Management Group<br />

(OMG). [Online]<br />

5. openArchitectureWare.<br />

http://www.openarchitectureware.org/. [Online]<br />

6. Teich J., Haubelt C. Digitale Hardware/Software-<br />

Systeme: Synthese und Optimierung. Berlin :<br />

Springer, 2007. 3540468226.<br />

7. Kesel F., Bartholomä R. Entwurf von digitalen<br />

Schaltungen und Systemen mit HDLs und FPGAs.<br />

s.l. : Ol<strong>de</strong>nbourg, 2006. 3486575562.<br />

MPC-Workshop, Juli 2009<br />

78

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)