Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Cache-Speicher für <strong>de</strong>n Softprozessor SIRIUS mit DDR-Interface<br />

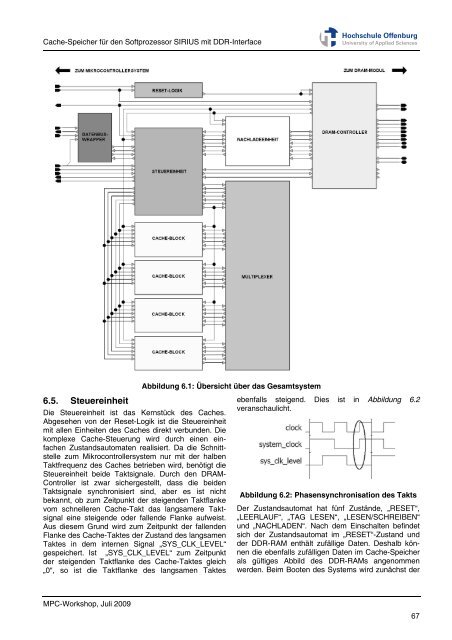

Abbildung 6.1: Übersicht über das Ges<strong>am</strong>tsystem<br />

6.5. Steuereinheit<br />

Die Steuereinheit ist das Kernstück <strong>de</strong>s Caches.<br />

Abgesehen von <strong>de</strong>r Reset-Logik ist die Steuereinheit<br />

mit allen Einheiten <strong>de</strong>s Caches direkt verbun<strong>de</strong>n. Die<br />

komplexe Cache-Steuerung wird durch einen einfachen<br />

Zustandsautomaten realisiert. Da die Schnittstelle<br />

zum Mikrocontrollersystem nur mit <strong>de</strong>r halben<br />

Taktfrequenz <strong>de</strong>s Caches betrieben wird, benötigt die<br />

Steuereinheit bei<strong>de</strong> Taktsignale. Durch <strong>de</strong>n DRAM-<br />

Controller ist zwar sichergestellt, dass die bei<strong>de</strong>n<br />

Taktsignale synchronisiert sind, aber es ist nicht<br />

bekannt, ob zum Zeitpunkt <strong>de</strong>r steigen<strong>de</strong>n Taktflanke<br />

vom schnelleren Cache-Takt das langs<strong>am</strong>ere Taktsignal<br />

eine steigen<strong>de</strong> o<strong>de</strong>r fallen<strong>de</strong> Flanke aufweist.<br />

Aus diesem Grund wird zum Zeitpunkt <strong>de</strong>r fallen<strong>de</strong>n<br />

Flanke <strong>de</strong>s Cache-Taktes <strong>de</strong>r Zustand <strong>de</strong>s langs<strong>am</strong>en<br />

Taktes in <strong>de</strong>m internen Signal „SYS_CLK_LEVEL“<br />

gespeichert. Ist „SYS_CLK_LEVEL“ zum Zeitpunkt<br />

<strong>de</strong>r steigen<strong>de</strong>n Taktflanke <strong>de</strong>s Cache-Taktes gleich<br />

„0“, so ist die Taktflanke <strong>de</strong>s langs<strong>am</strong>en Taktes<br />

ebenfalls steigend. Dies ist in Abbildung 6.2<br />

veranschaulicht.<br />

Abbildung 6.2: Phasensynchronisation <strong>de</strong>s Takts<br />

<strong>Der</strong> Zustandsautomat hat fünf Zustän<strong>de</strong>, „RESET“,<br />

„LEERLAUF“, „TAG LESEN“, „LESEN/SCHREIBEN“<br />

und „NACHLADEN“. Nach <strong>de</strong>m Einschalten befin<strong>de</strong>t<br />

sich <strong>de</strong>r Zustandsautomat im „RESET“-Zustand und<br />

<strong>de</strong>r DDR-RAM enthält zufällige Daten. Deshalb können<br />

die ebenfalls zufälligen Daten im Cache-Speicher<br />

als gültiges Abbild <strong>de</strong>s DDR-RAMs angenommen<br />

wer<strong>de</strong>n. Beim Booten <strong>de</strong>s Systems wird zunächst <strong>de</strong>r<br />

MPC-Workshop, Juli 2009<br />

67

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)