Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Neues von <strong>de</strong>r DATE 2009<br />

Es ist fraglich, ob europäische Unternehmen in<br />

Zukunft noch <strong>de</strong>n großen Aufwand für die neuen<br />

Fertigungsanlagen stemmen können.<br />

Neben diesen betriebswirtschaftlichen Aspekt, sind<br />

mit <strong>de</strong>r weiteren Strukturverkleinerung auch massive<br />

technische Probleme verbun<strong>de</strong>n.<br />

Die Strukturverkleinerung stößt inzwischen an die<br />

physikalischen Grenzen. Die Gate-Oxiddicke <strong>de</strong>r<br />

MOS-Transistoren beträgt nur noch etwa 1,5 nm, das<br />

sind 5 Atomlagen. Dadurch entstehen Leckströme<br />

sowohl durch das Gateoxid (Tunelstöme), als auch<br />

zwischen Drain und Source. D.h. das Gateoxid ist<br />

kein Isolator mehr und <strong>de</strong>r Transistor schaltet <strong>de</strong>n<br />

Drainstrom nicht mehr vollständig ab.<br />

Bild 2: Leckströme <strong>am</strong> MOS-Transistor [2]<br />

Die Leckströme treten verstärkt ab 65nm auf. Die<br />

Beherrschung dieser Leckströme wird zu einem<br />

Hauptproblem <strong>de</strong>r zukünftigen Technologie-<br />

Entwicklung.<br />

Wegen <strong>de</strong>r Gate-Leckströme muss das Gateoxid als<br />

Wi<strong>de</strong>rstand R gbd angesehen wer<strong>de</strong>n.<br />

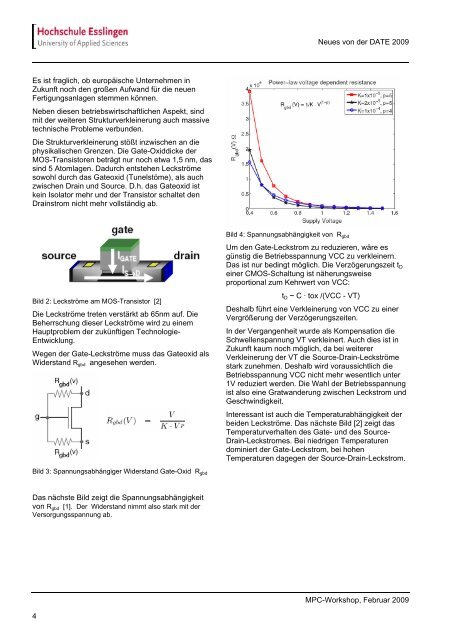

Bild 4: Spannungsabhängigkeit von R gbd<br />

Um <strong>de</strong>n Gate-Leckstrom zu reduzieren, wäre es<br />

günstig die Betriebsspannung VCC zu verkleinern.<br />

Das ist nur bedingt möglich. Die Verzögerungszeit t D<br />

einer CMOS-Schaltung ist näherungsweise<br />

proportional zum Kehrwert von VCC:<br />

t D ~ C · tox /(VCC - VT)<br />

Deshalb führt eine Verkleinerung von VCC zu einer<br />

Vergrößerung <strong>de</strong>r Verzögerungszeiten.<br />

In <strong>de</strong>r Vergangenheit wur<strong>de</strong> als Kompensation die<br />

Schwellenspannung VT verkleinert. Auch dies ist in<br />

Zukunft kaum noch möglich, da bei weiterer<br />

Verkleinerung <strong>de</strong>r VT die Source-Drain-Leckströme<br />

stark zunehmen. Deshalb wird voraussichtlich die<br />

Betriebsspannung VCC nicht mehr wesentlich unter<br />

1V reduziert wer<strong>de</strong>n. Die Wahl <strong>de</strong>r Betriebsspannung<br />

ist also eine Gratwan<strong>de</strong>rung zwischen Leckstrom und<br />

Geschwindigkeit.<br />

Interessant ist auch die Temperaturabhängigkeit <strong>de</strong>r<br />

bei<strong>de</strong>n Leckströme. Das nächste Bild [2] zeigt das<br />

Temperaturverhalten <strong>de</strong>s Gate- und <strong>de</strong>s Source-<br />

Drain-Leckstromes. Bei niedrigen Temperaturen<br />

dominiert <strong>de</strong>r Gate-Leckstrom, bei hohen<br />

Temperaturen dagegen <strong>de</strong>r Source-Drain-Leckstrom.<br />

Bild 3: Spannungsabhängiger Wi<strong>de</strong>rstand Gate-Oxid R gbd<br />

Das nächste Bild zeigt die Spannungsabhängigkeit<br />

von R gbd [1]. <strong>Der</strong> Wi<strong>de</strong>rstand nimmt also stark mit <strong>de</strong>r<br />

Versorgungsspannung ab.<br />

MPC-Workshop, Februar 2009<br />

4

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)