Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Prototyp <strong>eines</strong> digitalen EEGs auf Basis <strong>eines</strong> FPGAs<br />

für die Neurofeedbacksignalverarbeitung<br />

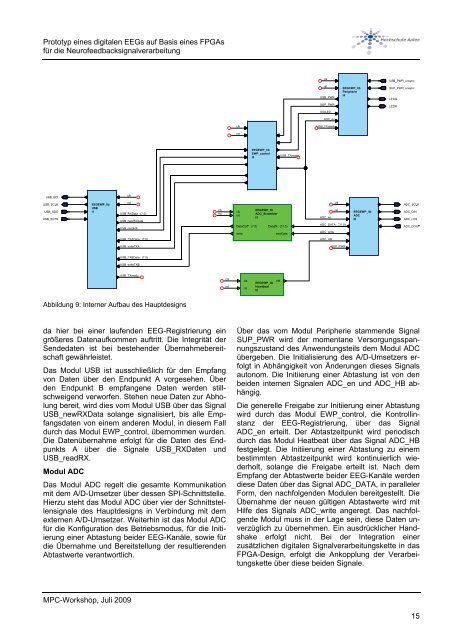

Abbildung 9: Interner Aufbau <strong>de</strong>s Haupt<strong>de</strong>signs<br />

da hier bei einer laufen<strong>de</strong>n EEG-Registrierung ein<br />

größeres Datenaufkommen auftritt. Die Integrität <strong>de</strong>r<br />

Sen<strong>de</strong>daten ist bei bestehen<strong>de</strong>r Übernahmebereitschaft<br />

gewährleistet.<br />

Das Modul USB ist ausschließlich für <strong>de</strong>n Empfang<br />

von Daten über <strong>de</strong>n Endpunkt A vorgesehen. Über<br />

<strong>de</strong>n Endpunkt B empfangene Daten wer<strong>de</strong>n stillschweigend<br />

verworfen. Stehen neue Daten zur Abholung<br />

bereit, wird dies vom Modul USB über das Signal<br />

USB_newRXData solange signalisiert, bis alle Empfangsdaten<br />

von einem an<strong>de</strong>ren Modul, in diesem Fall<br />

durch das Modul EWP_control, übernommen wur<strong>de</strong>n.<br />

Die Datenübernahme erfolgt für die Daten <strong>de</strong>s Endpunkts<br />

A über die Signale USB_RXDaten und<br />

USB_readRX.<br />

Modul ADC<br />

Das Modul ADC regelt die ges<strong>am</strong>te Kommunikation<br />

mit <strong>de</strong>m A/D-Umsetzer über <strong>de</strong>ssen SPI-Schnittstelle.<br />

Hierzu steht das Modul ADC über vier <strong>de</strong>r Schnittstellensignale<br />

<strong>de</strong>s Haupt<strong>de</strong>signs in Verbindung mit <strong>de</strong>m<br />

externen A/D-Umsetzer. Weiterhin ist das Modul ADC<br />

für die Konfiguration <strong>de</strong>s Betriebsmodus, für die Initiierung<br />

einer Abtastung bei<strong>de</strong>r EEG-Kanäle, sowie für<br />

die Übernahme und Bereitstellung <strong>de</strong>r resultieren<strong>de</strong>n<br />

Abtastwerte verantwortlich.<br />

Über das vom Modul Peripherie st<strong>am</strong>men<strong>de</strong> Signal<br />

SUP_PWR wird <strong>de</strong>r momentane Versorgungsspannungszustand<br />

<strong>de</strong>s Anwendungsteils <strong>de</strong>m Modul ADC<br />

übergeben. Die Initialisierung <strong>de</strong>s A/D-Umsetzers erfolgt<br />

in Abhängigkeit von Än<strong>de</strong>rungen dieses Signals<br />

autonom. Die Initiierung einer Abtastung ist von <strong>de</strong>n<br />

bei<strong>de</strong>n internen Signalen ADC_en und ADC_HB abhängig.<br />

Die generelle Freigabe zur Initiierung einer Abtastung<br />

wird durch das Modul EWP_control, die Kontrollinstanz<br />

<strong>de</strong>r EEG-Registrierung, über das Signal<br />

ADC_en erteilt. <strong>Der</strong> Abtastzeitpunkt wird periodisch<br />

durch das Modul Heatbeat über das Signal ADC_HB<br />

festgelegt. Die Initiierung einer Abtastung zu einem<br />

bestimmten Abtastzeitpunkt wird kontinuierlich wie<strong>de</strong>rholt,<br />

solange die Freigabe erteilt ist. Nach <strong>de</strong>m<br />

Empfang <strong>de</strong>r Abtastwerte bei<strong>de</strong>r EEG-Kanäle wer<strong>de</strong>n<br />

diese Daten über das Signal ADC_DATA, in paralleler<br />

Form, <strong>de</strong>n nachfolgen<strong>de</strong>n Modulen bereitgestellt. Die<br />

Übernahme <strong>de</strong>r neuen gültigen Abtastwerte wird mit<br />

Hilfe <strong>de</strong>s Signals ADC_write angeregt. Das nachfolgen<strong>de</strong><br />

Modul muss in <strong>de</strong>r Lage sein, diese Daten unverzüglich<br />

zu übernehmen. Ein ausdrücklicher Handshake<br />

erfolgt nicht. Bei <strong>de</strong>r Integration einer<br />

zusätzlichen digitalen Signalverarbeitungskette in das<br />

FPGA-<strong>Design</strong>, erfolgt die Ankopplung <strong>de</strong>r Verarbeitungskette<br />

über diese bei<strong>de</strong>n Signale.<br />

MPC-Workshop, Juli 2009<br />

15

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)