Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Neues von <strong>de</strong>r DATE 2009<br />

Rechenleistung erreicht als mit einem hochgetakteten<br />

Core und das bei geringerem Stromverbrauch.<br />

Allerdings erfor<strong>de</strong>rn Multi-Core-Architekturen auch<br />

eine feinkörnige Aufteilung <strong>de</strong>r Applikation auf die<br />

verschie<strong>de</strong>nen Cores, was aber bei Mobile Phones<br />

kein Problem ist.<br />

Das nächste Bild zeigt einen H.264(MPEG 4)-<br />

Deco<strong>de</strong>r-Chip <strong>de</strong>r Fa. Toshiba. <strong>Der</strong> Chip besteht aus<br />

8 Cores (32 Bit), jeweils mit einem L1-Cache. Die<br />

Cores sind über einen gemeins<strong>am</strong>en L2-Cache<br />

verbun<strong>de</strong>n. <strong>Der</strong> H.264-Algorithmus wird in einzelne<br />

Threads zerhackt und parallel auf <strong>de</strong>n verschie<strong>de</strong>nen<br />

Cores ausgeführt.<br />

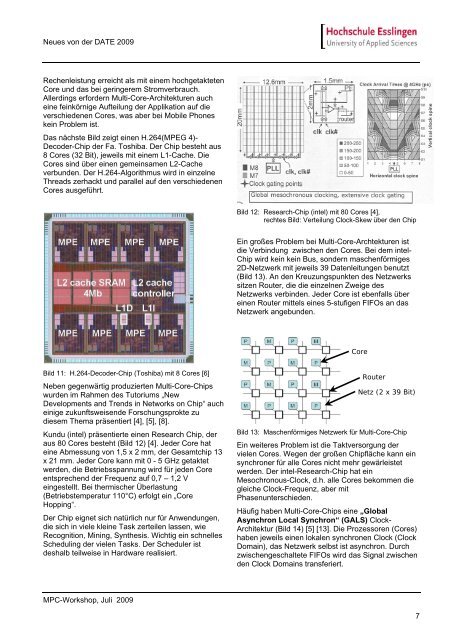

Bild 12: Research-Chip (intel) mit 80 Cores [4],<br />

rechtes Bild: Verteilung Clock-Skew über <strong>de</strong>n Chip<br />

Ein großes Problem bei Multi-Core-Archtekturen ist<br />

die Verbindung zwischen <strong>de</strong>n Cores. Bei <strong>de</strong>m intel-<br />

Chip wird kein kein Bus, son<strong>de</strong>rn maschenförmiges<br />

2D-Netzwerk mit jeweils 39 Datenleitungen benutzt<br />

(Bild 13). An <strong>de</strong>n Kreuzungspunkten <strong>de</strong>s Netzwerks<br />

sitzen Router, die die einzelnen Zweige <strong>de</strong>s<br />

Netzwerks verbin<strong>de</strong>n. Je<strong>de</strong>r Core ist ebenfalls über<br />

einen Router mittels <strong>eines</strong> 5-stufigen FIFOs an das<br />

Netzwerk angebun<strong>de</strong>n.<br />

Core<br />

Bild 11: H.264-Deco<strong>de</strong>r-Chip (Toshiba) mit 8 Cores [6]<br />

Neben gegenwärtig produzierten Multi-Core-Chips<br />

wur<strong>de</strong>n im Rahmen <strong>de</strong>s Tutoriums „New<br />

Developments and Trends in Networks on Chip“ auch<br />

einige zukunftsweisen<strong>de</strong> Forschungsprokte zu<br />

diesem Thema präsentiert [4], [5], [8].<br />

Kundu (intel) präsentierte einen Research Chip, <strong>de</strong>r<br />

aus 80 Cores besteht (Bild 12) [4]. Je<strong>de</strong>r Core hat<br />

eine Abmessung von 1,5 x 2 mm, <strong>de</strong>r Ges<strong>am</strong>tchip 13<br />

x 21 mm. Je<strong>de</strong>r Core kann mit 0 - 5 GHz getaktet<br />

wer<strong>de</strong>n, die Betriebsspannung wird für je<strong>de</strong>n Core<br />

entsprechend <strong>de</strong>r Frequenz auf 0,7 – 1,2 V<br />

eingestellt. Bei thermischer Überlastung<br />

(Betriebstemperatur 110°C) erfolgt ein „Core<br />

Hopping“.<br />

<strong>Der</strong> Chip eignet sich natürlich nur für Anwendungen,<br />

die sich in viele kleine Task zerteilen lassen, wie<br />

Recognition, Mining, Synthesis. Wichtig ein schnelles<br />

Scheduling <strong>de</strong>r vielen Tasks. <strong>Der</strong> Scheduler ist<br />

<strong>de</strong>shalb teilweise in Hardware realisiert.<br />

Router<br />

Netz (2 x 39 Bit)<br />

Bild 13: Maschenförmiges Netzwerk für Multi-Core-Chip<br />

Ein weiteres Problem ist die Taktversorgung <strong>de</strong>r<br />

vielen Cores. Wegen <strong>de</strong>r großen Chipfläche kann ein<br />

synchroner für alle Cores nicht mehr gewärleistet<br />

wer<strong>de</strong>n. <strong>Der</strong> intel-Research-Chip hat ein<br />

Mesochronous-Clock, d.h. alle Cores bekommen die<br />

gleiche Clock-Frequenz, aber mit<br />

Phasenunterschie<strong>de</strong>n.<br />

Häufig haben Multi-Core-Chips eine „Global<br />

Asynchron Local Synchron“ (GALS) Clock-<br />

Architektur (Bild 14) [5] [13]. Die Prozessoren (Cores)<br />

haben jeweils einen lokalen synchronen Clock (Clock<br />

Domain), das Netzwerk selbst ist asynchron. Durch<br />

zwischengeschaltete FIFOs wird das Signal zwischen<br />

<strong>de</strong>n Clock Domains transferiert.<br />

MPC-Workshop, Juli 2009<br />

7

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)