Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Cache-Speicher für <strong>de</strong>n Softprozessor SIRIUS mit DDR-Interface<br />

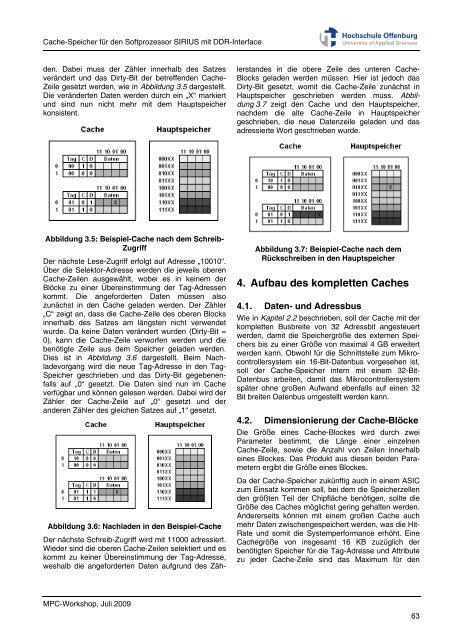

<strong>de</strong>n. Dabei muss <strong>de</strong>r Zähler innerhalb <strong>de</strong>s Satzes<br />

verän<strong>de</strong>rt und das Dirty-Bit <strong>de</strong>r betreffen<strong>de</strong>n Cache-<br />

Zeile gesetzt wer<strong>de</strong>n, wie in Abbildung 3.5 dargestellt.<br />

Die verän<strong>de</strong>rten Daten wer<strong>de</strong>n durch ein „X“ markiert<br />

und sind nun nicht mehr mit <strong>de</strong>m Hauptspeicher<br />

konsistent.<br />

<strong>Der</strong> nächste Schreib-Zugriff wird mit 11000 adressiert.<br />

Wie<strong>de</strong>r sind die oberen Cache-Zeilen selektiert und es<br />

kommt zu keiner Übereinstimmung <strong>de</strong>r Tag-Adresse,<br />

weshalb die angefor<strong>de</strong>rten Daten aufgrund <strong>de</strong>s Zählerstan<strong>de</strong>s<br />

in die obere Zeile <strong>de</strong>s unteren Cache-<br />

Blocks gela<strong>de</strong>n wer<strong>de</strong>n müssen. Hier ist jedoch das<br />

Dirty-Bit gesetzt, womit die Cache-Zeile zunächst in<br />

Hauptspeicher geschrieben wer<strong>de</strong>n muss. Abbildung<br />

3.7 zeigt <strong>de</strong>n Cache und <strong>de</strong>n Hauptspeicher,<br />

nach<strong>de</strong>m die alte Cache-Zeile in Hauptspeicher<br />

geschrieben, die neue Datenzeile gela<strong>de</strong>n und das<br />

adressierte Wort geschrieben wur<strong>de</strong>.<br />

Abbildung 3.5: <strong>Beispiel</strong>-Cache nach <strong>de</strong>m Schreib-<br />

Zugriff<br />

<strong>Der</strong> nächste Lese-Zugriff erfolgt auf Adresse „10010“.<br />

Über die Selektor-Adresse wer<strong>de</strong>n die jeweils oberen<br />

Cache-Zeilen ausgewählt, wobei es in keinem <strong>de</strong>r<br />

Blöcke zu einer Übereinstimmung <strong>de</strong>r Tag-Adressen<br />

kommt. Die angefor<strong>de</strong>rten Daten müssen also<br />

zunächst in <strong>de</strong>n Cache gela<strong>de</strong>n wer<strong>de</strong>n. <strong>Der</strong> Zähler<br />

„C“ zeigt an, dass die Cache-Zeile <strong>de</strong>s oberen Blocks<br />

innerhalb <strong>de</strong>s Satzes <strong>am</strong> längsten nicht verwen<strong>de</strong>t<br />

wur<strong>de</strong>. Da keine Daten verän<strong>de</strong>rt wur<strong>de</strong>n (Dirty-Bit =<br />

0), kann die Cache-Zeile verworfen wer<strong>de</strong>n und die<br />

benötigte Zeile aus <strong>de</strong>m Speicher gela<strong>de</strong>n wer<strong>de</strong>n.<br />

Dies ist in Abbildung 3.6 dargestellt. Beim Nachla<strong>de</strong>vorgang<br />

wird die neue Tag-Adresse in <strong>de</strong>n Tag-<br />

Speicher geschrieben und das Dirty-Bit gegebenenfalls<br />

auf „0“ gesetzt. Die Daten sind nun im Cache<br />

verfügbar und können gelesen wer<strong>de</strong>n. Dabei wird <strong>de</strong>r<br />

Zähler <strong>de</strong>r Cache-Zeile auf „0“ gesetzt und <strong>de</strong>r<br />

an<strong>de</strong>ren Zähler <strong>de</strong>s gleichen Satzes auf „1“ gesetzt.<br />

Abbildung 3.6: Nachla<strong>de</strong>n in <strong>de</strong>n <strong>Beispiel</strong>-Cache<br />

Abbildung 3.7: <strong>Beispiel</strong>-Cache nach <strong>de</strong>m<br />

Rückschreiben in <strong>de</strong>n Hauptspeicher<br />

4. Aufbau <strong>de</strong>s kompletten Caches<br />

4.1. Daten- und Adressbus<br />

Wie in Kapitel 2.2 beschrieben, soll <strong>de</strong>r Cache mit <strong>de</strong>r<br />

kompletten Busbreite von 32 Adressbit angesteuert<br />

wer<strong>de</strong>n, d<strong>am</strong>it die Speichergröße <strong>de</strong>s externen Speichers<br />

bis zu einer Größe von maximal 4 GB erweitert<br />

wer<strong>de</strong>n kann. Obwohl für die Schnittstelle zum Mikrocontrollersystem<br />

ein 16-Bit-Datenbus vorgesehen ist,<br />

soll <strong>de</strong>r Cache-Speicher intern mit einem 32-Bit-<br />

Datenbus arbeiten, d<strong>am</strong>it das Mikrocontrollersystem<br />

später ohne großen Aufwand ebenfalls auf einen 32<br />

Bit breiten Datenbus umgestellt wer<strong>de</strong>n kann.<br />

4.2. Dimensionierung <strong>de</strong>r Cache-Blöcke<br />

Die Größe <strong>eines</strong> Cache-Blockes wird durch zwei<br />

Par<strong>am</strong>eter bestimmt, die Länge einer einzelnen<br />

Cache-Zeile, sowie die Anzahl von Zeilen innerhalb<br />

<strong>eines</strong> Blockes. Das Produkt aus diesen bei<strong>de</strong>n Par<strong>am</strong>etern<br />

ergibt die Größe <strong>eines</strong> Blockes.<br />

Da <strong>de</strong>r Cache-Speicher zukünftig auch in einem ASIC<br />

zum Einsatz kommen soll, bei <strong>de</strong>m die Speicherzellen<br />

<strong>de</strong>n größten Teil <strong>de</strong>r Chipfläche benötigen, sollte die<br />

Größe <strong>de</strong>s Caches möglichst gering gehalten wer<strong>de</strong>n.<br />

An<strong>de</strong>rerseits können mit einem großen Cache auch<br />

mehr Daten zwischengespeichert wer<strong>de</strong>n, was die Hit-<br />

Rate und somit die Systemperformance erhöht. Eine<br />

Cachegröße von insges<strong>am</strong>t 16 KB zuzüglich <strong>de</strong>r<br />

benötigten Speicher für die Tag-Adresse und Attribute<br />

zu je<strong>de</strong>r Cache-Zeile sind das Maximum für <strong>de</strong>n<br />

MPC-Workshop, Juli 2009<br />

63

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)