Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Neues von <strong>de</strong>r DATE 2009<br />

Durch die obengenanten Maßnahmen können die<br />

Chipstrukturen auch in <strong>de</strong>n nächsten Jahren weiter<br />

verkleinert wer<strong>de</strong>n, bei beherrschbaren Leckströmen.<br />

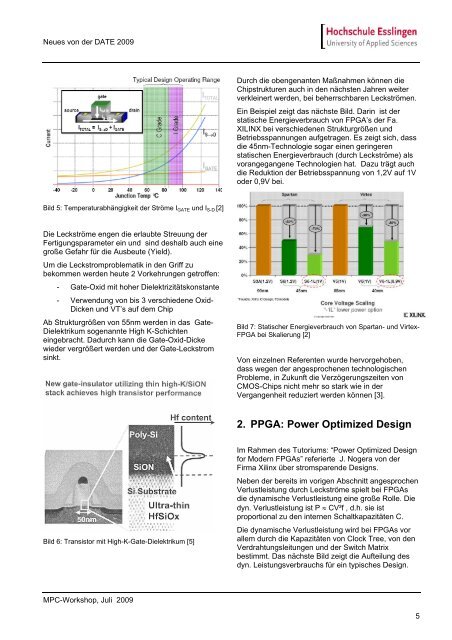

Ein <strong>Beispiel</strong> zeigt das nächste Bild. Darin ist <strong>de</strong>r<br />

statische Energieverbrauch von FPGA’s <strong>de</strong>r Fa.<br />

XILINX bei verschie<strong>de</strong>nen Strukturgrößen und<br />

Betriebsspannungen aufgetragen. Es zeigt sich, dass<br />

die 45nm-Technologie sogar einen geringeren<br />

statischen Energieverbrauch (durch Leckströme) als<br />

vorangegangene Technologien hat. Dazu trägt auch<br />

die Reduktion <strong>de</strong>r Betriebsspannung von 1,2V auf 1V<br />

o<strong>de</strong>r 0,9V bei.<br />

Bild 5: Temperaturabhängigkeit <strong>de</strong>r Ströme I GATE und I S-D [2]<br />

Die Leckströme engen die erlaubte Streuung <strong>de</strong>r<br />

Fertigungspar<strong>am</strong>eter ein und sind <strong>de</strong>shalb auch eine<br />

große Gefahr für die Ausbeute (Yield).<br />

Um die Leckstromproblematik in <strong>de</strong>n Griff zu<br />

bekommen wer<strong>de</strong>n heute 2 Vorkehrungen getroffen:<br />

- Gate-Oxid mit hoher Dielektrizitätskonstante<br />

- Verwendung von bis 3 verschie<strong>de</strong>ne Oxid-<br />

Dicken und VT’s auf <strong>de</strong>m Chip<br />

Ab Strukturgrößen von 55nm wer<strong>de</strong>n in das Gate-<br />

Dielektrikum sogenannte High K-Schichten<br />

eingebracht. Dadurch kann die Gate-Oxid-Dicke<br />

wie<strong>de</strong>r vergrößert wer<strong>de</strong>n und <strong>de</strong>r Gate-Leckstrom<br />

sinkt.<br />

Bild 7: Statischer Energieverbrauch von Spartan- und Virtex-<br />

FPGA bei Skalierung [2]<br />

Von einzelnen Referenten wur<strong>de</strong> hervorgehoben,<br />

dass wegen <strong>de</strong>r angesprochenen technologischen<br />

Probleme, in Zukunft die Verzögerungszeiten von<br />

CMOS-Chips nicht mehr so stark wie in <strong>de</strong>r<br />

Vergangenheit reduziert wer<strong>de</strong>n können [3].<br />

2. PPGA: Power Optimized <strong>Design</strong><br />

Bild 6: Transistor mit High-K-Gate-Dielektrikum [5]<br />

Im Rahmen <strong>de</strong>s Tutoriums: “Power Optimized <strong>Design</strong><br />

for Mo<strong>de</strong>rn FPGAs” referierte J. Nogera von <strong>de</strong>r<br />

Firma Xilinx über stromsparen<strong>de</strong> <strong>Design</strong>s.<br />

Neben <strong>de</strong>r bereits im vorigen Abschnitt angesprochen<br />

Verlustleistung durch Leckströme spielt bei FPGAs<br />

die dyn<strong>am</strong>ische Verlustleistung eine große Rolle. Die<br />

dyn. Verlustleistung ist P ≈ CV²f , d.h. sie ist<br />

proportional zu <strong>de</strong>n internen Schaltkapazitäten C.<br />

Die dyn<strong>am</strong>ische Verlustleistung wird bei FPGAs vor<br />

allem durch die Kapazitäten von Clock Tree, von <strong>de</strong>n<br />

Verdrahtungsleitungen und <strong>de</strong>r Switch Matrix<br />

bestimmt. Das nächste Bild zeigt die Aufteilung <strong>de</strong>s<br />

dyn. Leistungsverbrauchs für ein typisches <strong>Design</strong>.<br />

MPC-Workshop, Juli 2009<br />

5

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)