Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Open Source- / Freeware IC <strong>Design</strong> <strong>Flow</strong> <strong>am</strong> <strong>Beispiel</strong> einer DPLL<br />

Bild 5: Simulation DPLL: Steuerspannung<br />

Bild 9: VCO-Inverterstufe und Inverter<br />

Bild 6: DPLL: PLL eingerastet<br />

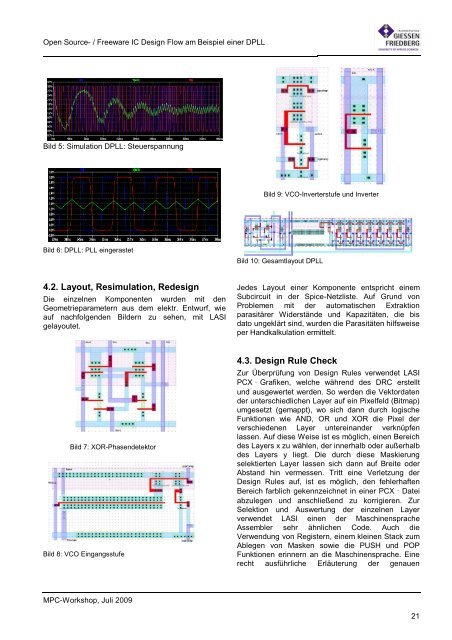

Bild 10: Ges<strong>am</strong>tlayout DPLL<br />

4.2. Layout, Resimulation, Re<strong>de</strong>sign<br />

Die einzelnen Komponenten wur<strong>de</strong>n mit <strong>de</strong>n<br />

Geometriepar<strong>am</strong>etern aus <strong>de</strong>m elektr. Entwurf, wie<br />

auf nachfolgen<strong>de</strong>n Bil<strong>de</strong>rn zu sehen, mit LASI<br />

gelayoutet.<br />

Je<strong>de</strong>s Layout einer Komponente entspricht einem<br />

Subcircuit in <strong>de</strong>r Spice-Netzliste. Auf Grund von<br />

Problemen mit <strong>de</strong>r automatischen Extraktion<br />

parasitärer Wi<strong>de</strong>rstän<strong>de</strong> und Kapazitäten, die bis<br />

dato ungeklärt sind, wur<strong>de</strong>n die Parasitäten hilfsweise<br />

per Handkalkulation ermittelt.<br />

Bild 7: XOR-Phasen<strong>de</strong>tektor<br />

Bild 8: VCO Eingangsstufe<br />

4.3. <strong>Design</strong> Rule Check<br />

Zur Überprüfung von <strong>Design</strong> Rules verwen<strong>de</strong>t LASI<br />

PCX‐Grafiken, welche während <strong>de</strong>s DRC erstellt<br />

und ausgewertet wer<strong>de</strong>n. So wer<strong>de</strong>n die Vektordaten<br />

<strong>de</strong>r unterschiedlichen Layer auf ein Pixelfeld (Bitmap)<br />

umgesetzt (gemappt), wo sich dann durch logische<br />

Funktionen wie AND, OR und XOR die Pixel <strong>de</strong>r<br />

verschie<strong>de</strong>nen Layer untereinan<strong>de</strong>r verknüpfen<br />

lassen. Auf diese Weise ist es möglich, einen Bereich<br />

<strong>de</strong>s Layers x zu wählen, <strong>de</strong>r innerhalb o<strong>de</strong>r außerhalb<br />

<strong>de</strong>s Layers y liegt. Die durch diese Maskierung<br />

selektierten Layer lassen sich dann auf Breite o<strong>de</strong>r<br />

Abstand hin vermessen. Tritt eine Verletzung <strong>de</strong>r<br />

<strong>Design</strong> Rules auf, ist es möglich, <strong>de</strong>n fehlerhaften<br />

Bereich farblich gekennzeichnet in einer PCX‐Datei<br />

abzulegen und anschließend zu korrigieren. Zur<br />

Selektion und Auswertung <strong>de</strong>r einzelnen Layer<br />

verwen<strong>de</strong>t LASI einen <strong>de</strong>r Maschinensprache<br />

Assembler sehr ähnlichen Co<strong>de</strong>. Auch die<br />

Verwendung von Registern, einem kleinen Stack zum<br />

Ablegen von Masken sowie die PUSH und POP<br />

Funktionen erinnern an die Maschinensprache. Eine<br />

recht ausführliche Erläuterung <strong>de</strong>r genauen<br />

MPC-Workshop, Juli 2009<br />

21

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)