Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Cache-Speicher für <strong>de</strong>n Softprozessor SIRIUS mit DDR-Interface<br />

gleiche Anzahl von Zeilen, wobei je<strong>de</strong> dieser Zeilen<br />

eine bestimmte Anzahl zus<strong>am</strong>menhängen<strong>de</strong>r Datenbytes<br />

enthält. Diese liegt üblicherweise im Bereich von<br />

4 bis 128 Bytes. [5]<br />

Besteht <strong>de</strong>r Cache nur aus einem Block, gibt es zwei<br />

verschie<strong>de</strong>ne Organisationstypen: „vollassoziativ“ und<br />

„direkt verdrahtet“. Bei einem vollassoziativen Cache<br />

kann je<strong>de</strong> Datenzeile aus <strong>de</strong>m großen Speicher an<br />

je<strong>de</strong>r beliebigen Stelle im Cache abgelegt wer<strong>de</strong>n. Bei<br />

einem direkt verdrahteten Cache kann je<strong>de</strong> Zeile,<br />

abhängig von <strong>de</strong>r Adresse, nur an einer einzigen<br />

Position gespeichert wer<strong>de</strong>n. Dadurch vereinfacht sich<br />

zwar <strong>de</strong>r Implementierungsaufwand, sobald jedoch<br />

nacheinan<strong>de</strong>r abwechselnd auf Speicherbereiche<br />

zugegriffen wird, die auf dieselbe Position im Cache<br />

verdrahtet sind, kommt es je<strong>de</strong>s Mal zu einem Miss.<br />

Um diesem Problem entgegenzuwirken, können<br />

mehrere direkt verdrahtete Cache-Blöcke parallel<br />

verwen<strong>de</strong>t wer<strong>de</strong>n. [5]<br />

Bei n Blöcken spricht man von einem n-fach assoziativen<br />

Cache. Je<strong>de</strong> Adresse ist auch hier mit einer<br />

bestimmten Zeile innerhalb <strong>eines</strong> Blockes verdrahtet,<br />

jedoch kann <strong>de</strong>r Block selbst frei gewählt wer<strong>de</strong>n.<br />

Somit ergeben sich für n Blöcke auch n mögliche<br />

Speicherpositionen im Cache. Diese n Speicherpositionen,<br />

die mit <strong>de</strong>nselben Adressen verdrahtet<br />

sind, wer<strong>de</strong>n als Satz bezeichnet. Die Anzahl <strong>de</strong>r<br />

Sätze in einem Cache ist gleich <strong>de</strong>r Anzahl <strong>de</strong>r Cache-<br />

Zeilen in einem Block. [5] Abbildung 3.2 zeigt einen n-<br />

fach assoziativen Cache mit m Sätzen.<br />

Abbildung 3.2: n-fach assoziativer Cache mit m<br />

Sätzen<br />

Für die Entwicklung <strong>de</strong>s Caches war vorgegeben,<br />

dass <strong>de</strong>r Cache 4-fach assoziativ ausgelegt sein soll.<br />

D<strong>am</strong>it ist sichergestellt, dass min<strong>de</strong>stens vier<br />

unterschiedliche Datenbereiche gleichzeitig zwischengespeichert<br />

wer<strong>de</strong>n können. Außer<strong>de</strong>m stellt dies<br />

einen guten Kompromiss aus Effizienz und Implementierungsaufwand<br />

dar.<br />

3.3. Adressierung und Steuerung<br />

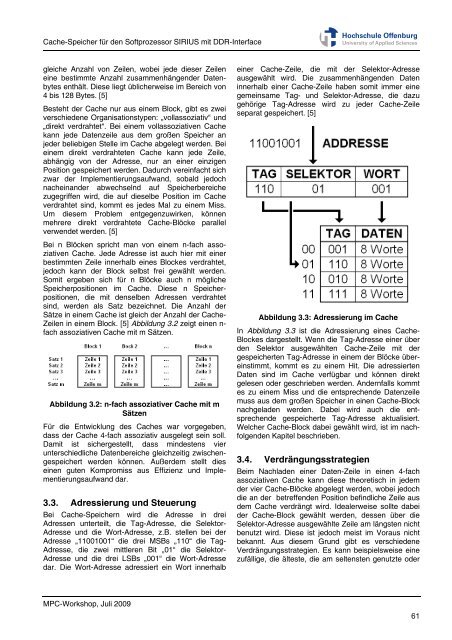

Bei Cache-Speichern wird die Adresse in drei<br />

Adressen unterteilt, die Tag-Adresse, die Selektor-<br />

Adresse und die Wort-Adresse, z.B. stellen bei <strong>de</strong>r<br />

Adresse „11001001“ die drei MSBs „110“ die Tag-<br />

Adresse, die zwei mittleren Bit „01“ die Selektor-<br />

Adresse und die drei LSBs „001“ die Wort-Adresse<br />

dar. Die Wort-Adresse adressiert ein Wort innerhalb<br />

einer Cache-Zeile, die mit <strong>de</strong>r Selektor-Adresse<br />

ausgewählt wird. Die zus<strong>am</strong>menhängen<strong>de</strong>n Daten<br />

innerhalb einer Cache-Zeile haben somit immer eine<br />

gemeins<strong>am</strong>e Tag- und Selektor-Adresse, die dazu<br />

gehörige Tag-Adresse wird zu je<strong>de</strong>r Cache-Zeile<br />

separat gespeichert. [5]<br />

Abbildung 3.3: Adressierung im Cache<br />

In Abbildung 3.3 ist die Adressierung <strong>eines</strong> Cache-<br />

Blockes dargestellt. Wenn die Tag-Adresse einer über<br />

<strong>de</strong>n Selektor ausgewählten Cache-Zeile mit <strong>de</strong>r<br />

gespeicherten Tag-Adresse in einem <strong>de</strong>r Blöcke übereinstimmt,<br />

kommt es zu einem Hit. Die adressierten<br />

Daten sind im Cache verfügbar und können direkt<br />

gelesen o<strong>de</strong>r geschrieben wer<strong>de</strong>n. An<strong>de</strong>rnfalls kommt<br />

es zu einem Miss und die entsprechen<strong>de</strong> Datenzeile<br />

muss aus <strong>de</strong>m großen Speicher in einen Cache-Block<br />

nachgela<strong>de</strong>n wer<strong>de</strong>n. Dabei wird auch die entsprechen<strong>de</strong><br />

gespeicherte Tag-Adresse aktualisiert.<br />

Welcher Cache-Block dabei gewählt wird, ist im nachfolgen<strong>de</strong>n<br />

Kapitel beschrieben.<br />

3.4. Verdrängungsstrategien<br />

Beim Nachla<strong>de</strong>n einer Daten-Zeile in einen 4-fach<br />

assoziativen Cache kann diese theoretisch in je<strong>de</strong>m<br />

<strong>de</strong>r vier Cache-Blöcke abgelegt wer<strong>de</strong>n, wobei jedoch<br />

die an <strong>de</strong>r betreffen<strong>de</strong>n Position befindliche Zeile aus<br />

<strong>de</strong>m Cache verdrängt wird. I<strong>de</strong>alerweise sollte dabei<br />

<strong>de</strong>r Cache-Block gewählt wer<strong>de</strong>n, <strong>de</strong>ssen über die<br />

Selektor-Adresse ausgewählte Zeile <strong>am</strong> längsten nicht<br />

benutzt wird. Diese ist jedoch meist im Voraus nicht<br />

bekannt. Aus diesem Grund gibt es verschie<strong>de</strong>ne<br />

Verdrängungsstrategien. Es kann beispielsweise eine<br />

zufällige, die älteste, die <strong>am</strong> seltensten genutzte o<strong>de</strong>r<br />

MPC-Workshop, Juli 2009<br />

61

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)