Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Dimensionierung und Entwurfszentrierung analoger Schaltungen mit WiCkeD<br />

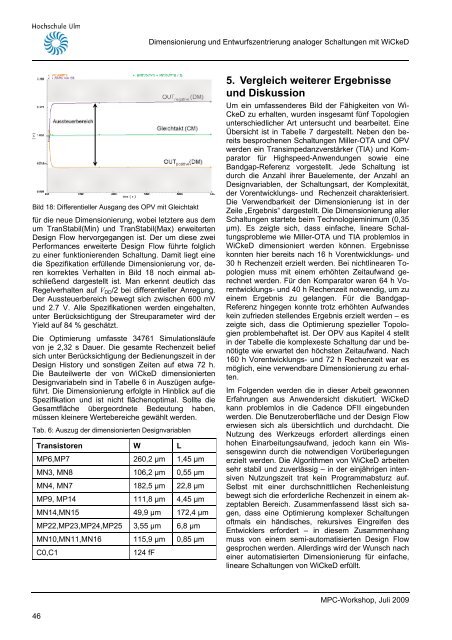

Bild 18: Differentieller Ausgang <strong>de</strong>s OPV mit Gleichtakt<br />

für die neue Dimensionierung, wobei letztere aus <strong>de</strong>m<br />

um TranStabil(Min) und TranStabil(Max) erweiterten<br />

<strong>Design</strong> <strong>Flow</strong> hervorgegangen ist. <strong>Der</strong> um diese zwei<br />

Performances erweiterte <strong>Design</strong> <strong>Flow</strong> führte folglich<br />

zu einer funktionieren<strong>de</strong>n Schaltung. D<strong>am</strong>it liegt eine<br />

die Spezifikation erfüllen<strong>de</strong> Dimensionierung vor, <strong>de</strong>ren<br />

korrektes Verhalten in Bild 18 noch einmal abschließend<br />

dargestellt ist. Man erkennt <strong>de</strong>utlich das<br />

Regelverhalten auf V DD /2 bei differentieller Anregung.<br />

<strong>Der</strong> Aussteuerbereich bewegt sich zwischen 600 mV<br />

und 2.7 V. Alle Spezifikationen wer<strong>de</strong>n eingehalten,<br />

unter Berücksichtigung <strong>de</strong>r Streupar<strong>am</strong>eter wird <strong>de</strong>r<br />

Yield auf 84 % geschätzt.<br />

Die Optimierung umfasste 34761 Simulationsläufe<br />

von je 2,32 s Dauer. Die ges<strong>am</strong>te Rechenzeit belief<br />

sich unter Berücksichtigung <strong>de</strong>r Bedienungszeit in <strong>de</strong>r<br />

<strong>Design</strong> History und sonstigen Zeiten auf etwa 72 h.<br />

Die Bauteilwerte <strong>de</strong>r von WiCkeD dimensionierten<br />

<strong>Design</strong>variabeln sind in Tabelle 6 in Auszügen aufgeführt.<br />

Die Dimensionierung erfolgte in Hinblick auf die<br />

Spezifikation und ist nicht flächenoptimal. Sollte die<br />

Ges<strong>am</strong>tfläche übergeordnete Be<strong>de</strong>utung haben,<br />

müssen kleinere Wertebereiche gewählt wer<strong>de</strong>n.<br />

Tab. 6: Auszug <strong>de</strong>r dimensionierten <strong>Design</strong>variablen<br />

Transistoren W L<br />

MP6,MP7 260,2 µm 1,45 µm<br />

MN3, MN8 106,2 µm 0,55 µm<br />

MN4, MN7 182,5 µm 22,8 µm<br />

MP9, MP14 111,8 µm 4,45 µm<br />

MN14,MN15 49,9 µm 172,4 µm<br />

MP22,MP23,MP24,MP25 3,55 µm 6,8 µm<br />

MN10,MN11,MN16 115,9 µm 0,85 µm<br />

C0,C1<br />

124 fF<br />

5. Vergleich weiterer Ergebnisse<br />

und Diskussion<br />

Um ein umfassen<strong>de</strong>res Bild <strong>de</strong>r Fähigkeiten von Wi-<br />

CkeD zu erhalten, wur<strong>de</strong>n insges<strong>am</strong>t fünf Topologien<br />

unterschiedlicher Art untersucht und bearbeitet. Eine<br />

Übersicht ist in Tabelle 7 dargestellt. Neben <strong>de</strong>n bereits<br />

besprochenen Schaltungen Miller-OTA und OPV<br />

wer<strong>de</strong>n ein Transimpedanzverstärker (TIA) und Komparator<br />

für Highspeed-Anwendungen sowie eine<br />

Bandgap-Referenz vorgestellt. Je<strong>de</strong> Schaltung ist<br />

durch die Anzahl ihrer Bauelemente, <strong>de</strong>r Anzahl an<br />

<strong>Design</strong>variablen, <strong>de</strong>r Schaltungsart, <strong>de</strong>r Komplexität,<br />

<strong>de</strong>r Vorentwicklungs- und Rechenzeit charakterisiert.<br />

Die Verwendbarkeit <strong>de</strong>r Dimensionierung ist in <strong>de</strong>r<br />

Zeile „Ergebnis“ dargestellt. Die Dimensionierung aller<br />

Schaltungen startete beim Technologieminimum (0,35<br />

µm). Es zeigte sich, dass einfache, lineare Schaltungsprobleme<br />

wie Miller-OTA und TIA problemlos in<br />

WiCkeD dimensioniert wer<strong>de</strong>n können. Ergebnisse<br />

konnten hier bereits nach 16 h Vorentwicklungs- und<br />

30 h Rechenzeit erzielt wer<strong>de</strong>n. Bei nichtlinearen Topologien<br />

muss mit einem erhöhten Zeitaufwand gerechnet<br />

wer<strong>de</strong>n. Für <strong>de</strong>n Komparator waren 64 h Vorentwicklungs-<br />

und 40 h Rechenzeit notwendig, um zu<br />

einem Ergebnis zu gelangen. Für die Bandgap-<br />

Referenz hingegen konnte trotz erhöhten Aufwan<strong>de</strong>s<br />

kein zufrie<strong>de</strong>n stellen<strong>de</strong>s Ergebnis erzielt wer<strong>de</strong>n – es<br />

zeigte sich, dass die Optimierung spezieller Topologien<br />

problembehaftet ist. <strong>Der</strong> OPV aus Kapitel 4 stellt<br />

in <strong>de</strong>r Tabelle die komplexeste Schaltung dar und benötigte<br />

wie erwartet <strong>de</strong>n höchsten Zeitaufwand. Nach<br />

160 h Vorentwicklungs- und 72 h Rechenzeit war es<br />

möglich, eine verwendbare Dimensionierung zu erhalten.<br />

Im Folgen<strong>de</strong>n wer<strong>de</strong>n die in dieser Arbeit gewonnen<br />

Erfahrungen aus Anwen<strong>de</strong>rsicht diskutiert. WiCkeD<br />

kann problemlos in die Ca<strong>de</strong>nce DFII eingebun<strong>de</strong>n<br />

wer<strong>de</strong>n. Die Benutzeroberfläche und <strong>de</strong>r <strong>Design</strong> <strong>Flow</strong><br />

erwiesen sich als übersichtlich und durchdacht. Die<br />

Nutzung <strong>de</strong>s Werkzeugs erfor<strong>de</strong>rt allerdings einen<br />

hohen Einarbeitungsaufwand, jedoch kann ein Wissensgewinn<br />

durch die notwendigen Vorüberlegungen<br />

erzielt wer<strong>de</strong>n. Die Algorithmen von WiCkeD arbeiten<br />

sehr stabil und zuverlässig – in <strong>de</strong>r einjährigen intensiven<br />

Nutzungszeit trat kein Progr<strong>am</strong>mabsturz auf.<br />

Selbst mit einer durchschnittlichen Rechenleistung<br />

bewegt sich die erfor<strong>de</strong>rliche Rechenzeit in einem akzeptablen<br />

Bereich. Zus<strong>am</strong>menfassend lässt sich sagen,<br />

dass eine Optimierung komplexer Schaltungen<br />

oftmals ein händisches, rekursives Eingreifen <strong>de</strong>s<br />

Entwicklers erfor<strong>de</strong>rt – in diesem Zus<strong>am</strong>menhang<br />

muss von einem semi-automatisierten <strong>Design</strong> <strong>Flow</strong><br />

gesprochen wer<strong>de</strong>n. Allerdings wird <strong>de</strong>r Wunsch nach<br />

einer automatisierten Dimensionierung für einfache,<br />

lineare Schaltungen von WiCkeD erfüllt.<br />

MPC-Workshop, Juli 2009<br />

46

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)