Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Cache-Speicher für <strong>de</strong>n Softprozessor SIRIUS mit DDR-Interface.<br />

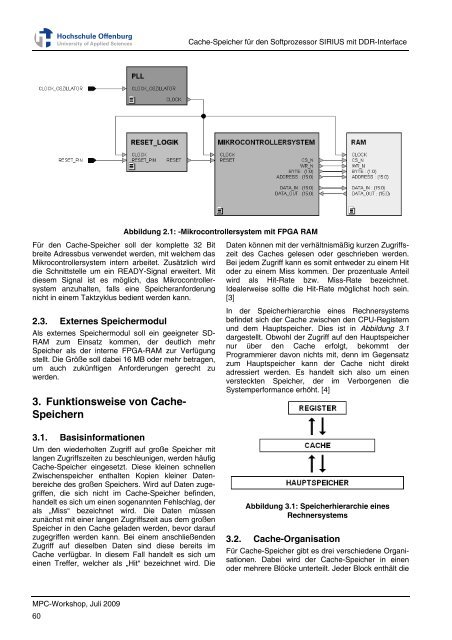

Abbildung 2.1: -Mikrocontrollersystem mit FPGA RAM<br />

Für <strong>de</strong>n Cache-Speicher soll <strong>de</strong>r komplette 32 Bit<br />

breite Adressbus verwen<strong>de</strong>t wer<strong>de</strong>n, mit welchem das<br />

Mikrocontrollersystem intern arbeitet. Zusätzlich wird<br />

die Schnittstelle um ein READY-Signal erweitert. Mit<br />

diesem Signal ist es möglich, das Mikrocontrollersystem<br />

anzuhalten, falls eine Speicheranfor<strong>de</strong>rung<br />

nicht in einem Taktzyklus bedient wer<strong>de</strong>n kann.<br />

2.3. Externes Speichermodul<br />

Als externes Speichermodul soll ein geeigneter SD-<br />

RAM zum Einsatz kommen, <strong>de</strong>r <strong>de</strong>utlich mehr<br />

Speicher als <strong>de</strong>r interne FPGA-RAM zur Verfügung<br />

stellt. Die Größe soll dabei 16 MB o<strong>de</strong>r mehr betragen,<br />

um auch zukünftigen Anfor<strong>de</strong>rungen gerecht zu<br />

wer<strong>de</strong>n.<br />

3. Funktionsweise von Cache-<br />

Speichern<br />

3.1. Basisinformationen<br />

Um <strong>de</strong>n wie<strong>de</strong>rholten Zugriff auf große Speicher mit<br />

langen Zugriffszeiten zu beschleunigen, wer<strong>de</strong>n häufig<br />

Cache-Speicher eingesetzt. Diese kleinen schnellen<br />

Zwischenspeicher enthalten Kopien kleiner Datenbereiche<br />

<strong>de</strong>s großen Speichers. Wird auf Daten zugegriffen,<br />

die sich nicht im Cache-Speicher befin<strong>de</strong>n,<br />

han<strong>de</strong>lt es sich um einen sogenannten Fehlschlag, <strong>de</strong>r<br />

als „Miss“ bezeichnet wird. Die Daten müssen<br />

zunächst mit einer langen Zugriffszeit aus <strong>de</strong>m großen<br />

Speicher in <strong>de</strong>n Cache gela<strong>de</strong>n wer<strong>de</strong>n, bevor darauf<br />

zugegriffen wer<strong>de</strong>n kann. Bei einem anschließen<strong>de</strong>n<br />

Zugriff auf dieselben Daten sind diese bereits im<br />

Cache verfügbar. In diesem Fall han<strong>de</strong>lt es sich um<br />

einen Treffer, welcher als „Hit“ bezeichnet wird. Die<br />

Daten können mit <strong>de</strong>r verhältnismäßig kurzen Zugriffszeit<br />

<strong>de</strong>s Caches gelesen o<strong>de</strong>r geschrieben wer<strong>de</strong>n.<br />

Bei je<strong>de</strong>m Zugriff kann es somit entwe<strong>de</strong>r zu einem Hit<br />

o<strong>de</strong>r zu einem Miss kommen. <strong>Der</strong> prozentuale Anteil<br />

wird als Hit-Rate bzw. Miss-Rate bezeichnet.<br />

I<strong>de</strong>alerweise sollte die Hit-Rate möglichst hoch sein.<br />

[3]<br />

In <strong>de</strong>r Speicherhierarchie <strong>eines</strong> Rechnersystems<br />

befin<strong>de</strong>t sich <strong>de</strong>r Cache zwischen <strong>de</strong>n CPU-Registern<br />

und <strong>de</strong>m Hauptspeicher. Dies ist in Abbildung 3.1<br />

dargestellt. Obwohl <strong>de</strong>r Zugriff auf <strong>de</strong>n Hauptspeicher<br />

nur über <strong>de</strong>n Cache erfolgt, bekommt <strong>de</strong>r<br />

Progr<strong>am</strong>mierer davon nichts mit, <strong>de</strong>nn im Gegensatz<br />

zum Hauptspeicher kann <strong>de</strong>r Cache nicht direkt<br />

adressiert wer<strong>de</strong>n. Es han<strong>de</strong>lt sich also um einen<br />

versteckten Speicher, <strong>de</strong>r im Verborgenen die<br />

Systemperformance erhöht. [4]<br />

Abbildung 3.1: Speicherhierarchie <strong>eines</strong><br />

Rechnersystems<br />

3.2. Cache-Organisation<br />

Für Cache-Speicher gibt es drei verschie<strong>de</strong>ne Organisationen.<br />

Dabei wird <strong>de</strong>r Cache-Speicher in einen<br />

o<strong>de</strong>r mehrere Blöcke unterteilt. Je<strong>de</strong>r Block enthält die<br />

MPC-Workshop, Juli 2009<br />

60

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)