Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Cache-Speicher für <strong>de</strong>n Softprozessor SIRIUS mit DDR-Interface.<br />

untere Speicherbereich beschrieben. Um das unnötige<br />

Nachla<strong>de</strong>n aus <strong>de</strong>m DDR-RAM von zufälligen Daten<br />

zu vermei<strong>de</strong>n, wer<strong>de</strong>n die Daten im Cache als Abbild<br />

<strong>de</strong>s unteren Speicherbereichs angenommen. Dazu<br />

müssen im „RESET“-Zustand die Tag-Adressen und<br />

Attribute <strong>de</strong>r Tag-Speicher korrekt initialisiert wer<strong>de</strong>n.<br />

Mit <strong>de</strong>n vier Cache-Blöcken, die je 4 KB Daten<br />

zwischenspeichern, können die unteren 16 KB Daten<br />

abgebil<strong>de</strong>t wer<strong>de</strong>n. Dies entspricht <strong>de</strong>m Adressraum<br />

von 0x00000000 bis 0x00003FFF. Dies ergibt für die<br />

Cache-Blöcke folgen<strong>de</strong> Adressbereiche:<br />

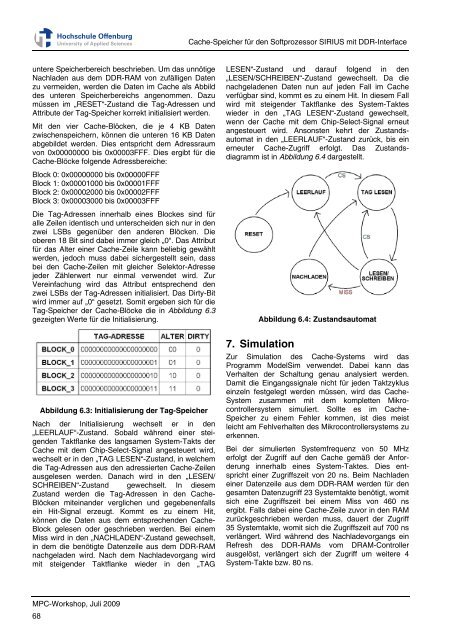

LESEN“-Zustand und darauf folgend in <strong>de</strong>n<br />

„LESEN/SCHREIBEN“-Zustand gewechselt. Da die<br />

nachgela<strong>de</strong>nen Daten nun auf je<strong>de</strong>n Fall im Cache<br />

verfügbar sind, kommt es zu einem Hit. In diesem Fall<br />

wird mit steigen<strong>de</strong>r Taktflanke <strong>de</strong>s System-Taktes<br />

wie<strong>de</strong>r in <strong>de</strong>n „TAG LESEN“-Zustand gewechselt,<br />

wenn <strong>de</strong>r Cache mit <strong>de</strong>m Chip-Select-Signal erneut<br />

angesteuert wird. Ansonsten kehrt <strong>de</strong>r Zustandsautomat<br />

in <strong>de</strong>n „LEERLAUF“-Zustand zurück, bis ein<br />

erneuter Cache-Zugriff erfolgt. Das Zustandsdiagr<strong>am</strong>m<br />

ist in Abbildung 6.4 dargestellt.<br />

Block 0: 0x00000000 bis 0x00000FFF<br />

Block 1: 0x00001000 bis 0x00001FFF<br />

Block 2: 0x00002000 bis 0x00002FFF<br />

Block 3: 0x00003000 bis 0x00003FFF<br />

Die Tag-Adressen innerhalb <strong>eines</strong> Blockes sind für<br />

alle Zeilen i<strong>de</strong>ntisch und unterschei<strong>de</strong>n sich nur in <strong>de</strong>n<br />

zwei LSBs gegenüber <strong>de</strong>n an<strong>de</strong>ren Blöcken. Die<br />

oberen 18 Bit sind dabei immer gleich „0“. Das Attribut<br />

für das Alter einer Cache-Zeile kann beliebig gewählt<br />

wer<strong>de</strong>n, jedoch muss dabei sichergestellt sein, dass<br />

bei <strong>de</strong>n Cache-Zeilen mit gleicher Selektor-Adresse<br />

je<strong>de</strong>r Zählerwert nur einmal verwen<strong>de</strong>t wird. Zur<br />

Vereinfachung wird das Attribut entsprechend <strong>de</strong>n<br />

zwei LSBs <strong>de</strong>r Tag-Adressen initialisiert. Das Dirty-Bit<br />

wird immer auf „0“ gesetzt. Somit ergeben sich für die<br />

Tag-Speicher <strong>de</strong>r Cache-Blöcke die in Abbildung 6.3<br />

gezeigten Werte für die Initialisierung.<br />

Abbildung 6.4: Zustandsautomat<br />

Abbildung 6.3: Initialisierung <strong>de</strong>r Tag-Speicher<br />

Nach <strong>de</strong>r Initialisierung wechselt er in <strong>de</strong>n<br />

„LEERLAUF“-Zustand. Sobald während einer steigen<strong>de</strong>n<br />

Taktflanke <strong>de</strong>s langs<strong>am</strong>en System-Takts <strong>de</strong>r<br />

Cache mit <strong>de</strong>m Chip-Select-Signal angesteuert wird,<br />

wechselt er in <strong>de</strong>n „TAG LESEN“-Zustand, in welchem<br />

die Tag-Adressen aus <strong>de</strong>n adressierten Cache-Zeilen<br />

ausgelesen wer<strong>de</strong>n. Danach wird in <strong>de</strong>n „LESEN/<br />

SCHREIBEN“-Zustand gewechselt. In diesem<br />

Zustand wer<strong>de</strong>n die Tag-Adressen in <strong>de</strong>n Cache-<br />

Blöcken miteinan<strong>de</strong>r verglichen und gegebenenfalls<br />

ein Hit-Signal erzeugt. Kommt es zu einem Hit,<br />

können die Daten aus <strong>de</strong>m entsprechen<strong>de</strong>n Cache-<br />

Block gelesen o<strong>de</strong>r geschrieben wer<strong>de</strong>n. Bei einem<br />

Miss wird in <strong>de</strong>n „NACHLADEN“-Zustand gewechselt,<br />

in <strong>de</strong>m die benötigte Datenzeile aus <strong>de</strong>m DDR-RAM<br />

nachgela<strong>de</strong>n wird. Nach <strong>de</strong>m Nachla<strong>de</strong>vorgang wird<br />

mit steigen<strong>de</strong>r Taktflanke wie<strong>de</strong>r in <strong>de</strong>n „TAG<br />

7. Simulation<br />

Zur Simulation <strong>de</strong>s Cache-Systems wird das<br />

Progr<strong>am</strong>m Mo<strong>de</strong>lSim verwen<strong>de</strong>t. Dabei kann das<br />

Verhalten <strong>de</strong>r Schaltung genau analysiert wer<strong>de</strong>n.<br />

D<strong>am</strong>it die Eingangssignale nicht für je<strong>de</strong>n Taktzyklus<br />

einzeln festgelegt wer<strong>de</strong>n müssen, wird das Cache-<br />

System zus<strong>am</strong>men mit <strong>de</strong>m kompletten Mikrocontrollersystem<br />

simuliert. Sollte es im Cache-<br />

Speicher zu einem Fehler kommen, ist dies meist<br />

leicht <strong>am</strong> Fehlverhalten <strong>de</strong>s Mikrocontrollersystems zu<br />

erkennen.<br />

Bei <strong>de</strong>r simulierten Systemfrequenz von 50 MHz<br />

erfolgt <strong>de</strong>r Zugriff auf <strong>de</strong>n Cache gemäß <strong>de</strong>r Anfor<strong>de</strong>rung<br />

innerhalb <strong>eines</strong> System-Taktes. Dies entspricht<br />

einer Zugriffszeit von 20 ns. Beim Nachla<strong>de</strong>n<br />

einer Datenzeile aus <strong>de</strong>m DDR-RAM wer<strong>de</strong>n für <strong>de</strong>n<br />

ges<strong>am</strong>ten Datenzugriff 23 Systemtakte benötigt, womit<br />

sich eine Zugriffszeit bei einem Miss von 460 ns<br />

ergibt. Falls dabei eine Cache-Zeile zuvor in <strong>de</strong>n RAM<br />

zurückgeschrieben wer<strong>de</strong>n muss, dauert <strong>de</strong>r Zugriff<br />

35 Systemtakte, womit sich die Zugriffszeit auf 700 ns<br />

verlängert. Wird während <strong>de</strong>s Nachla<strong>de</strong>vorgangs ein<br />

Refresh <strong>de</strong>s DDR-RAMs vom DRAM-Controller<br />

ausgelöst, verlängert sich <strong>de</strong>r Zugriff um weitere 4<br />

System-Takte bzw. 80 ns.<br />

MPC-Workshop, Juli 2009<br />

68

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)