Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Der UMC 0.18 Design Flow am Beispiel eines PDA ... - Mpc.belwue.de

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

„Entwurf <strong>eines</strong> High-Speed Multiplexers/Demultiplexers für einen Mischer in<br />

0,35µm Technologie“<br />

die Parallelschaltung ergibt sich dann wie<strong>de</strong>r ein<br />

geringerer Durchgangswi<strong>de</strong>rstand R ON.<br />

Daraus ergibt sich folgen<strong>de</strong>s Schaltbild (Abb.9):<br />

Abbildung 9: Schaltbild<br />

Transmissiongate<br />

5. Simulation <strong>de</strong>r kompletten<br />

Schaltung<br />

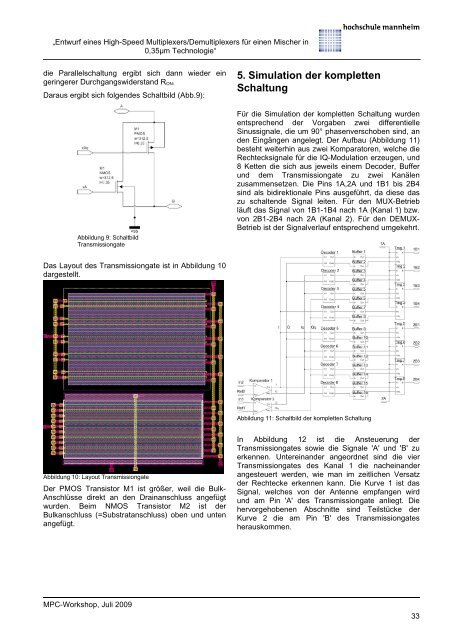

Für die Simulation <strong>de</strong>r kompletten Schaltung wur<strong>de</strong>n<br />

entsprechend <strong>de</strong>r Vorgaben zwei differentielle<br />

Sinussignale, die um 90° phasenverschoben sind, an<br />

<strong>de</strong>n Eingängen angelegt. <strong>Der</strong> Aufbau (Abbildung 11)<br />

besteht weiterhin aus zwei Komparatoren, welche die<br />

Rechtecksignale für die IQ-Modulation erzeugen, und<br />

8 Ketten die sich aus jeweils einem Deco<strong>de</strong>r, Buffer<br />

und <strong>de</strong>m Transmissiongate zu zwei Kanälen<br />

zus<strong>am</strong>mensetzen. Die Pins 1A,2A und 1B1 bis 2B4<br />

sind als bidirektionale Pins ausgeführt, da diese das<br />

zu schalten<strong>de</strong> Signal leiten. Für <strong>de</strong>n MUX-Betrieb<br />

läuft das Signal von 1B1-1B4 nach 1A (Kanal 1) bzw.<br />

von 2B1-2B4 nach 2A (Kanal 2). Für <strong>de</strong>n DEMUX-<br />

Betrieb ist <strong>de</strong>r Signalverlauf entsprechend umgekehrt.<br />

Das Layout <strong>de</strong>s Transmissiongate ist in Abbildung 10<br />

dargestellt.<br />

Abbildung 11: Schaltbild <strong>de</strong>r kompletten Schaltung<br />

Abbildung 10: Layout Transmissiongate<br />

<strong>Der</strong> PMOS Transistor M1 ist größer, weil die Bulk-<br />

Anschlüsse direkt an <strong>de</strong>n Drainanschluss angefügt<br />

wur<strong>de</strong>n. Beim NMOS Transistor M2 ist <strong>de</strong>r<br />

Bulkanschluss (=Substratanschluss) oben und unten<br />

angefügt.<br />

In Abbildung 12 ist die Ansteuerung <strong>de</strong>r<br />

Transmissiongates sowie die Signale 'A' und 'B' zu<br />

erkennen. Untereinan<strong>de</strong>r angeordnet sind die vier<br />

Transmissiongates <strong>de</strong>s Kanal 1 die nacheinan<strong>de</strong>r<br />

angesteuert wer<strong>de</strong>n, wie man im zeitlichen Versatz<br />

<strong>de</strong>r Rechtecke erkennen kann. Die Kurve 1 ist das<br />

Signal, welches von <strong>de</strong>r Antenne empfangen wird<br />

und <strong>am</strong> Pin 'A' <strong>de</strong>s Transmissiongate anliegt. Die<br />

hervorgehobenen Abschnitte sind Teilstücke <strong>de</strong>r<br />

Kurve 2 die <strong>am</strong> Pin 'B' <strong>de</strong>s Transmissiongates<br />

herauskommen.<br />

MPC-Workshop, Juli 2009<br />

33

![[Geben Sie hier die Überschrift ein] - MPC](https://img.yumpu.com/8654082/1/188x260/geben-sie-hier-die-uberschrift-ein-mpc.jpg?quality=85)