You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

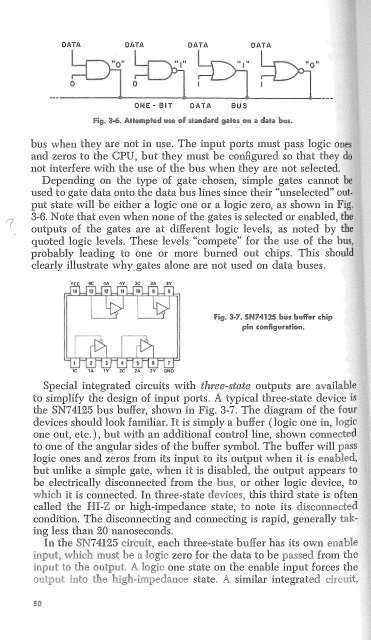

DATA DATA DATA DATA<br />

ONE - BIT DATA BUS<br />

bus they are not in use. The input ports must pass logic o<br />

and zeros to the CPU, but they must be configured. so that they<br />

not interfere with the use of the bus when they are not selected.<br />

Depending on the type of gate chosen, simple gates cannot<br />

used to gate data onto the data bus lines since their "unselected" ou<br />

put state will be either a logic one or a logic zero, as shown in F<br />

3-6. Note that even when none of the gates is selected or enabled, t<br />

outputs of the gates are at different logic levels, as noted by t<br />

quoted logic levels. These levels "compete" for the use of the b<br />

probably leading to one or more burned out chips. This shou<br />

clearly illustrate why gates alone are not used on data buses.<br />

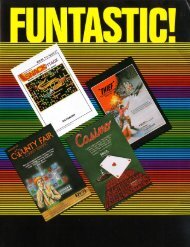

Vee 4C 4A 4Y 3A 3Y<br />

l'i. :!l-7. !1174125 b11s i>uffe• d1i1><br />

pi11 e@rofo91nati11.<br />

1C 1A 1Y 2C 2A 2V GNO<br />

Special integrated circuits with three-state outputs are<br />

to simplify the design of input ports. A typical three-state device<br />

the SN74125 bus buffer, shown in Fig. 3-7. The diagram of the<br />

devices should look familiar. It is simply a buffer (logic one in, logi<br />

one out, etc. ) , but an additional control line, shown<br />

l:o one of the angular sides of the buffer symbol The buffer will<br />

logic ones and zeros from its input to its output when it is vuau'•''<br />

but unlike a simple gate, when it is disabled, the output appears<br />

be electrically disconnected from the or other logic device, to<br />

it is connected. In three-state devices. this third state is often<br />

called the HI-Z or high-impedance state, to note its d.i:scc)rn1e(;te'C1<br />

condition. The disconnecting and connecting is rapid, generally<br />

ing less than 20 nanoseconds.<br />

In the SI"-J7 4125 each three-state buffer has its own<br />

zero for the data to be from the<br />

one state on the enable input forces the<br />

5'.tate. A similar integratsd.