Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

MULTIPLE FLAGS<br />

Many systems have a number of Hags that must be checked<br />

regular basis. In some cases, a priority must be established, s<br />

some devices are more important, or require faster attention, tha<br />

others. The priority is easily set in the program, since the orde<br />

which the various bits are tested determines which devices are "<br />

viced" before others. The program steps shown in Example 4-6<br />

check several flag bits in sequence, from bit D7 to bit D5, provi<br />

a priority in the order in which the corresponding devices would<br />

serviced by the computer.<br />

In this example, the flag for bit D7 was detected when it w<br />

logic one, while the other two flags were detected when they w<br />

logic zero. Other bit-sensing steps may be added for other flags,<br />

the order in which the bits are tested may be changed at any ti<br />

simply by changing the program to reflect the new order. Note<br />

the data involved in the AND operation is not changed, and it o<br />

needs to be input from the input port at the start of the sequence<br />

instructions.<br />

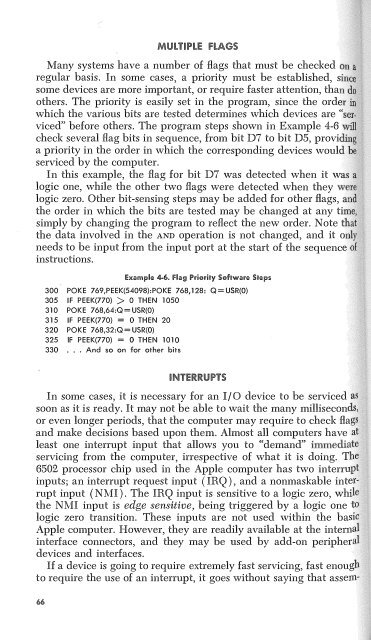

Example 4-6. Flag Priority Software Steps<br />

300 POKE 769,PEEK(54098):POKE 768,128: Q=USR(O)<br />

305 IF PEEK(770) > 0 THEN l 050<br />

310 POKE 768,64:Q=USR(O)<br />

315 IF PEEK(770) = 0 THEN 20<br />

320 POKE 768,32:Q=USR(O)<br />

325 IF PEEK(770) = 0 THEN 1010<br />

330 . . • And so on for other bits<br />

INTERRUPTS<br />

In some cases, it is necessary for an 1/0 device to be serviced<br />

soon as it is ready. It may not be able to wait the many millisecon<br />

or even longer periods, that the computer may require to check Ha<br />

and make decisions based upon them. Almost all computers have<br />

least one interrupt input that allows you to "demand" immedia<br />

servicing from the computer, irrespective of what it is doing. T<br />

6502 processor chip used in the Apple computer has two interru<br />

inputs; an interrupt request input ( IRQ), and a nonmaskable inte<br />

rupt input ( NMI). The IRQ input is sensitive to a logic zero, whi<br />

the NMI input is edge sensitive, being triggered by a logic one<br />

logic zero transition. These inputs are not used within the bas·<br />

Apple computer. However, they are readily available at the intern<br />

interface connectors, and they may be used by add-on peripher<br />

devices and interfaces.<br />

If a device is going to require extremely fast servicing, fast enoug<br />

to require the use of an interrupt, it goes without saying that asse<br />

66