Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

cal AND<br />

pointer.<br />

subroutine has been loaded, along with the three-b<br />

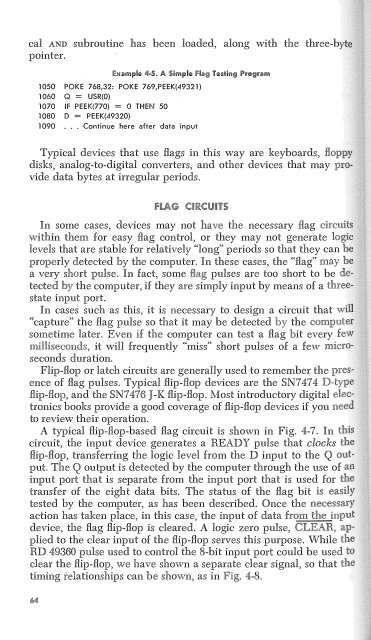

F.xampie -11·5. A l&imple fis Teoti1111 !'rogrnm<br />

1050 POKE 768,32: POKE 769,PEEK(49321)<br />

1060 Q = USR(O)<br />

1070 IF PEEK(770) = 0 THEN 50<br />

1080 D = PEEK(49320)<br />

1090 . . . Continue here after data input<br />

Typical devices that use flags in this way are keyboards, Hopp<br />

disks, analog-to-digital converters, and other devices that may pro<br />

vide data bytes at irregular periods.<br />

In some cases, devices may not the necessary .flag circuit<br />

within them for easy :flag control, or they may not generate logic<br />

levels that are stable for relatively "long" periods so that they can be<br />

properly detected by the computer. In these cases, the "flag"<br />

a very short pulse. In fact, some pulses are too short to be<br />

tected by the computer, if they are simply input by means of a<br />

state input port<br />

In cases such as this, it is necessary to design a circuit that<br />

"capture" the flag pulse SO that it may be detected the vV,CH!_)UC,JL<br />

sometime later. Even if the computer can test a flag bit every<br />

milHsecods, it will frequently "miss" short pulses of a few micro"<br />

seconds duration.<br />

Flip-flop or latch circuits are generally used to remember the<br />

ence of flag pulses. Typical flip-fl.op devices are the SN7474<br />

Hip-fl.op, and the SN7476 J-K flip-flop. Most introductory digital<br />

tronics books provide a good coverage of flip-flop devices if you<br />

to review their operation.<br />

A typical flip-Hop-based flag circuit is shown in Fig. 4-7. In<br />

circuit, the input device generates a READY pulse that clocks<br />

flip-flop, transferring the logic level from the D input to the Q<br />

put. The Q output is detected by the computer through the use of<br />

input pmt that is separate from the input port that is used for th{)<br />

transfer of the eight data bits. The status of the flag bit<br />

tested by the computer, as has been described. Once the ne,ces:sai,·y<br />

action has taken place, in this case, the input of data<br />

device, the flag flip-flop is cleared. A logic zero pulse,<br />

plied to the clear input of the flip-flop serves this purpose. While<br />

RD 49360 pulse used to control the 8-bit input port could be used to<br />

dear the flip-flop, we have shown a separate clear signal, so that the<br />

timing relationships can be shown, as in 4-8.