TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

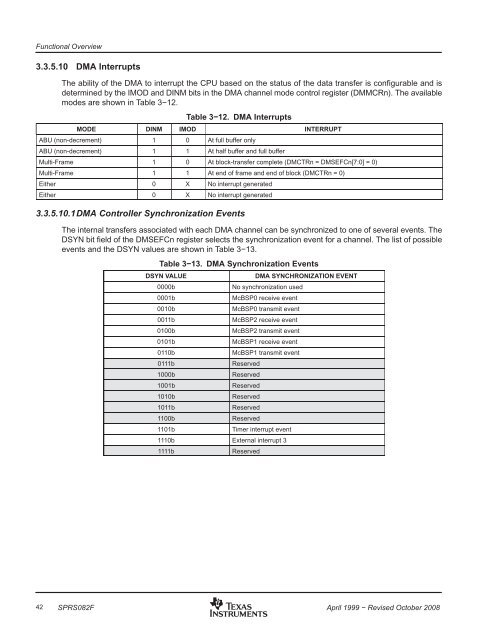

Functional Overview3.3.5.10 DMA InterruptsThe ability of the DMA to interrupt the CPU based on the status of the data transfer is configurable and isdetermined by the IMOD and DINM bits in the DMA channel mode control register (DMMCRn). The availablemodes are shown in Table 3−12.Table 3−12. DMA InterruptsMODE DINM IMOD INTERRUPTABU (non-decrement) 1 0 At full buffer onlyABU (non-decrement) 1 1 At half buffer and full bufferMulti-Frame 1 0 At block-transfer complete (DMCTRn = DMSEFCn[7:0] = 0)Multi-Frame 1 1 At end of frame and end of block (DMCTRn = 0)Either 0 X No interrupt generatedEither 0 X No interrupt generated3.3.5.10.1DMA Controller Synchronization EventsThe internal transfers associated with each DMA channel can be synchronized to one of several events. TheDSYN bit field of the DMSEFCn register selects the synchronization event for a channel. The list of possibleevents and the DSYN values are shown in Table 3−13.Table 3−13. DMA Synchronization EventsDSYN VALUEDMA SYNCHRONIZATION EVENT0000bNo synchronization used0001bMcBSP0 receive event0010bMcBSP0 transmit event0011bMcBSP2 receive event0100bMcBSP2 transmit event0101bMcBSP1 receive event0110bMcBSP1 transmit event0111bReserved1000bReserved1001bReserved1010bReserved1011bReserved1100bReserved1101bTimer interrupt event1110b External interrupt 31111bReserved42 SPRS082FApril 1999 − Revised October 2008