TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

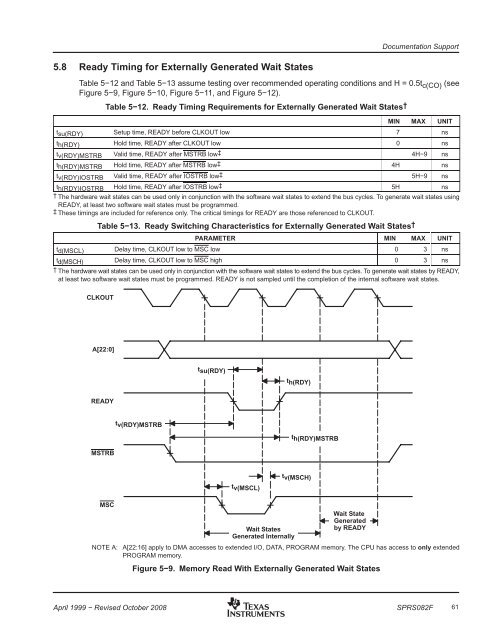

Documentation Support5.8 Ready Timing for Externally Generated Wait StatesTable 5−12 and Table 5−13 assume testing over recommended operating conditions and H = 0.5t c(CO) (seeFigure 5−9, Figure 5−10, Figure 5−11, and Figure 5−12).Table 5−12. Ready Timing Requirements for Externally Generated Wait States †MIN MAX UNITtsu(RDY) Setup time, READY before CLKOUT low 7 nsth(RDY) Hold time, READY after CLKOUT low 0 nstv(RDY)MSTRB Valid time, READY after MSTRB low‡ 4H−9 nsth(RDY)MSTRB Hold time, READY after MSTRB low‡ 4H nstv(RDY)IOSTRB Valid time, READY after IOSTRB low‡ 5H−9 nsth(RDY)IOSTRB Hold time, READY after IOSTRB low‡ 5H ns† The hardware wait states can be used only in conjunction with the software wait states to extend the bus cycles. To generate wait states usingREADY, at least two software wait states must be programmed.‡ These timings are included for reference only. The critical timings for READY are those referenced to CLKOUT.Table 5−13. Ready Switching Characteristics for Externally Generated Wait States †PARAMETER MIN MAX UNITtd(MSCL) Delay time, CLKOUT low to MSC low 0 3 nstd(MSCH) Delay time, CLKOUT low to MSC high 0 3 ns† The hardware wait states can be used only in conjunction with the software wait states to extend the bus cycles. To generate wait states by READY,at least two software wait states must be programmed. READY is not sampled until the completion of the internal software wait states.CLKOUTA[22:0]tsu(RDY)th(RDY)READYMSTRBtv(RDY)MSTRBth(RDY)MSTRBtv(MSCL)tv(MSCH)MSCWait StatesGenerated InternallyWait StateGeneratedby READYNOTE A: A[22:16] apply to DMA accesses to extended I/O, DATA, PROGRAM memory. The CPU has access to only extendedPROGRAM memory.Figure 5−9. Memory Read With Externally Generated Wait StatesApril 1999 − Revised October 2008SPRS082F61