TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

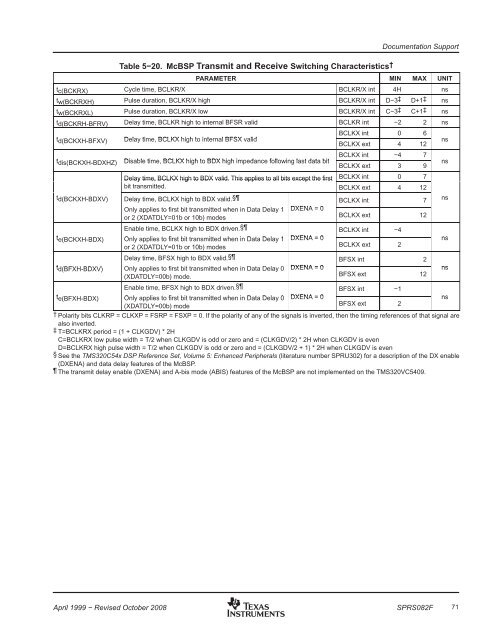

Table 5−20. McBSP Transmit and Receive Switching Characteristics †Documentation SupportPARAMETER MIN MAX UNITtc(BCKRX) Cycle time, BCLKR/X BCLKR/X int 4H nstw(BCKRXH) Pulse duration, BCLKR/X high BCLKR/X int D−3‡ D+1‡ nstw(BCKRXL) Pulse duration, BCLKR/X low BCLKR/X int C−3‡ C+1‡ nstd(BCKRH-BFRV) Delay time, BCLKR high to internal BFSR valid BCLKR int −2 2 nstd(BCKXH-BFXV)tdis(BCKXH-BDXHZ)Delay time, BCLKX high to internal BFSX validDisable time, BCLKX high to BDX high impedance following last data bitBCLKX int 0 6BCLKX ext 4 12BCLKX int −4 7BCLKX ext 3 9Delay time, BCLKX high to BDX valid. This applies to all bits except the first BCLKX int 0 7bit transmitted. BCLKX ext 4 12td(BCKXH-BDXV) Delay time, BCLKX high to BDX valid.§BCLKX int 7nsOnly applies to first bit transmitted when in Data Delay 1DXENA = 0or 2 (XDATDLY=01b or 10b) modesBCLKX ext 12Enable time, BCLKX high to BDX driven.§BCLKX int −4te(BCKXH-BDX) Only applies to first bit transmitted when in Data Delay 1DXENA = 0nsor 2 (XDATDLY=01b or 10b) modesBCLKX ext 2Delay time, BFSX high to BDX valid.§BFSX int 2td(BFXH-BDXV) Only applies to first bit transmitted when in Data Delay 0DXENA = 0ns(XDATDLY=00b) mode.BFSX ext 12Enable time, BFSX high to BDX driven.§BFSX int −1te(BFXH-BDX) Only applies to first bit transmitted when in Data Delay 0DXENA = 0ns(XDATDLY=00b) modeBFSX ext 2† Polarity bits CLKRP = CLKXP = FSRP = FSXP = 0. If the polarity of any of the signals is inverted, then the timing references of that signal arealso inverted.‡ T=BCLKRX period = (1 + CLKGDV) * 2HC=BCLKRX low pulse width = T/2 when CLKGDV is odd or zero and = (CLKGDV/2) * 2H when CLKGDV is evenD=BCLKRX high pulse width = T/2 when CLKGDV is odd or zero and = (CLKGDV/2 + 1) * 2H when CLKGDV is even§ See the TMS320C54x DSP Reference Set, Volume 5: Enhanced Peripherals (literature number SPRU302) for a description of the DX enable(DXENA) and data delay features of the McBSP. The transmit delay enable (DXENA) and A-bis mode (ABIS) features of the McBSP are not implemented on the <strong>TMS320VC5409</strong>.nsnsApril 1999 − Revised October 2008SPRS082F71