TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

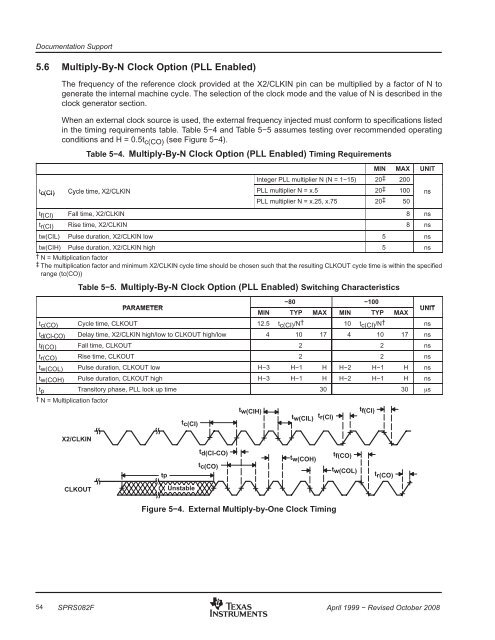

Documentation Support5.6 Multiply-By-N Clock Option (PLL Enabled)The frequency of the reference clock provided at the X2/CLKIN pin can be multiplied by a factor of N togenerate the internal machine cycle. The selection of the clock mode and the value of N is described in theclock generator section.When an external clock source is used, the external frequency injected must conform to specifications listedin the timing requirements table. Table 5−4 and Table 5−5 assumes testing over recommended operatingconditions and H = 0.5t c(CO) (see Figure 5−4).Table 5−4. Multiply-By-N Clock Option (PLL Enabled) Timing RequirementsMIN MAX UNITInteger PLL multiplier N (N = 1−15) 20‡ 200tc(CI)Cycle time, X2/CLKINPLL multiplier N = x.5 20‡ 100 nsPLL multiplier N = x.25, x.75 20‡ 50tf(CI) Fall time, X2/CLKIN 8 nstr(CI) Rise time, X2/CLKIN 8 nstw(CIL) Pulse duration, X2/CLKIN low 5 nstw(CIH) Pulse duration, X2/CLKIN high 5 ns† N = Multiplication factor‡ The multiplication factor and minimum X2/CLKIN cycle time should be chosen such that the resulting CLKOUT cycle time is within the specifiedrange (tc(CO))Table 5−5. Multiply-By-N Clock Option (PLL Enabled) Switching Characteristics−80−100PARAMETERUNITMIN TYP MAX MIN TYP MAXtc(CO) Cycle time, CLKOUT 12.5 tc(CI)/N† 10 tc(CI)/N† nstd(CI-CO) Delay time, X2/CLKIN high/low to CLKOUT high/low 4 10 17 4 10 17 nstf(CO) Fall time, CLKOUT 2 2 nstr(CO) Rise time, CLKOUT 2 2 nstw(COL) Pulse duration, CLKOUT low H−3 H−1 H H−2 H−1 H nstw(COH) Pulse duration, CLKOUT high H−3 H−1 H H−2 H−1 H nstp Transitory phase, PLL lock up time 30 30 s† N = Multiplication factorX2/CLKINtc(CI)tw(CIH)tw(CIL)tr(CI)tf(CI)tptd(CI-CO)tc(CO)tw(COH)tf(CO)tw(COL)tr(CO)CLKOUTUnstableFigure 5−4. External Multiply-by-One Clock Timing54 SPRS082FApril 1999 − Revised October 2008