TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

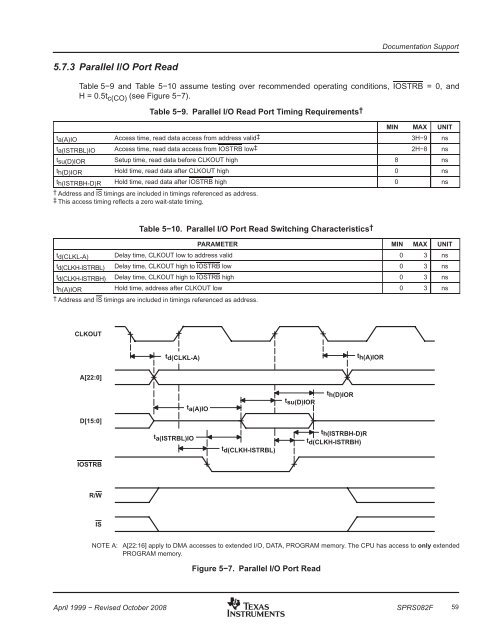

Documentation Support5.7.3 Parallel I/O Port ReadTable 5−9 and Table 5−10 assume testing over recommended operating conditions, IOSTRB = 0, andH = 0.5t c(CO) (see Figure 5−7).Table 5−9. Parallel I/O Read Port Timing Requirements † MIN MAX UNITta(A)IO Access time, read data access from address valid‡ 3H−9 nsta(ISTRBL)IO Access time, read data access from IOSTRB low‡ 2H−8 nstsu(D)IOR Setup time, read data before CLKOUT high 8 nsth(D)IOR Hold time, read data after CLKOUT high 0 nsth(ISTRBH-D)R Hold time, read data after IOSTRB high 0 ns† Address and IS timings are included in timings referenced as address.‡ This access timing reflects a zero wait-state timing.Table 5−10. Parallel I/O Port Read Switching Characteristics †PARAMETER MIN MAX UNITtd(CLKL-A) Delay time, CLKOUT low to address valid 0 3 nstd(CLKH-ISTRBL) Delay time, CLKOUT high to IOSTRB low 0 3 nstd(CLKH-ISTRBH) Delay time, CLKOUT high to IOSTRB high 0 3 nsth(A)IOR Hold time, address after CLKOUT low 0 3 ns† Address and IS timings are included in timings referenced as address.CLKOUTtd(CLKL-A)th(A)IORA[22:0]ta(A)IOtsu(D)IORth(D)IORD[15:0]ta(ISTRBL)IOtd(CLKH-ISTRBL)th(ISTRBH-D)Rtd(CLKH-ISTRBH)IOSTRBR/WISNOTE A: A[22:16] apply to DMA accesses to extended I/O, DATA, PROGRAM memory. The CPU has access to only extendedPROGRAM memory.Figure 5−7. Parallel I/O Port ReadApril 1999 − Revised October 2008SPRS082F59