TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

TMS320VC5409 Fixed-Point Digital Signal ... - Texas Instruments

- No tags were found...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

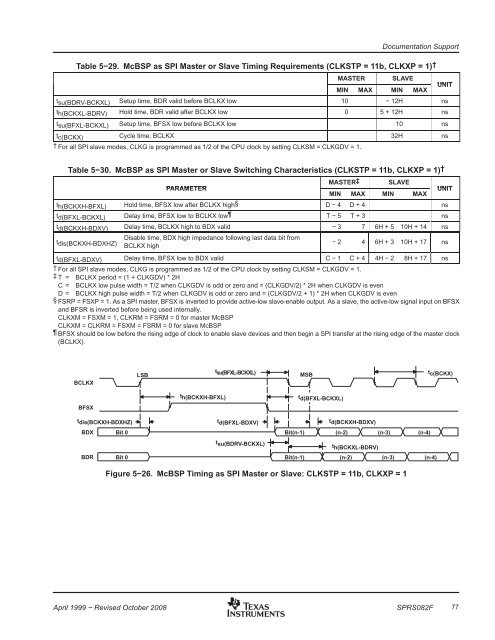

Documentation SupportTable 5−29. McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 1) †MASTER SLAVEMIN MAX MIN MAXUNITtsu(BDRV-BCKXL) Setup time, BDR valid before BCLKX low 10 − 12H nsth(BCKXL-BDRV) Hold time, BDR valid after BCLKX low 0 5 + 12H nstsu(BFXL-BCKXL) Setup time, BFSX low before BCLKX low 10 nstc(BCKX) Cycle time, BCLKX 32H ns† For all SPI slave modes, CLKG is programmed as 1/2 of the CPU clock by setting CLKSM = CLKGDV = 1.Table 5−30. McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 1) †PARAMETERMASTER‡SLAVEMIN MAX MIN MAXth(BCKXH-BFXL) Hold time, BFSX low after BCLKX high§ D − 4 D + 4 nstd(BFXL-BCKXL) Delay time, BFSX low to BCLKX low T − 5 T + 3 nstd(BCKXH-BDXV) Delay time, BCLKX high to BDX valid − 3 7 6H + 5 10H + 14 nstdis(BCKXH-BDXHZ)Disable time, BDX high impedance following last data bit fromBCLKX highUNIT− 2 4 6H + 3 10H + 17 nstd(BFXL-BDXV) Delay time, BFSX low to BDX valid C − 1 C + 4 4H − 2 8H + 17 ns† For all SPI slave modes, CLKG is programmed as 1/2 of the CPU clock by setting CLKSM = CLKGDV = 1.‡ T = BCLKX period = (1 + CLKGDV) * 2HC = BCLKX low pulse width = T/2 when CLKGDV is odd or zero and = (CLKGDV/2) * 2H when CLKGDV is evenD = BCLKX high pulse width = T/2 when CLKGDV is odd or zero and = (CLKGDV/2 + 1) * 2H when CLKGDV is even§ FSRP = FSXP = 1. As a SPI master, BFSX is inverted to provide active-low slave-enable output. As a slave, the active-low signal input on BFSXand BFSR is inverted before being used internally.CLKXM = FSXM = 1, CLKRM = FSRM = 0 for master McBSPCLKXM = CLKRM = FSXM = FSRM = 0 for slave McBSP BFSX should be low before the rising edge of clock to enable slave devices and then begin a SPI transfer at the rising edge of the master clock(BCLKX).BCLKXLSBt su(BFXL-BCKXL)MSBtc(BCKX)t d(BFXL-BCKXL)BFSXt h(BCKXH-BFXL)t dis(BCKXH-BDXHZ) t d(BFXL-BDXV)t d(BCKXH-BDXV)BDX Bit 0 Bit(n-1) (n-2) (n-3) (n-4)t su(BDRV-BCKXL)t h(BCKXL-BDRV)BDR Bit 0 Bit(n-1) (n-2) (n-3) (n-4)Figure 5−26. McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1April 1999 − Revised October 2008SPRS082F77