research activities in 2007 - CSEM

research activities in 2007 - CSEM

research activities in 2007 - CSEM

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Programmable Multi-Processor Eng<strong>in</strong>e for Ultra-Low-Power S<strong>in</strong>gle-Chip DVB Receiver<br />

C. Arm, P.-D. Pfister, F. Rampogna, Ch. Ruppert • , A. Duret •<br />

A family of System-On-Chip (SoC) circuits implement<strong>in</strong>g terrestrial mobile digital TV (DVB-T/H) receivers as s<strong>in</strong>gle-die solutions requir<strong>in</strong>g very few<br />

external components has been developed and is be<strong>in</strong>g produced by the <strong>in</strong>dustrial partner of this project. The use of ultra-low-power programmable<br />

DSPs for the implementation of the Orthogonal Frequency Division Multiplex (OFDM) demodulation and adaptive channel estimation/correction<br />

allows an automatic adaptation of the receiver to the fast-chang<strong>in</strong>g reception conditions encountered <strong>in</strong> mobile receivers<br />

<strong>CSEM</strong> is participat<strong>in</strong>g <strong>in</strong> a CTI/KTI project whose goal is to<br />

develop modem core <strong>in</strong>tellectual property (IP) support<strong>in</strong>g<br />

multiple broadband wireless OFDM modulations (DAB, DVB,<br />

T-DMB, MediaFlo, etc.). The core is architectured as a<br />

software def<strong>in</strong>ed radio implement<strong>in</strong>g a multiprocessor<br />

architecture based on <strong>CSEM</strong> Macgic ® DSP core [1] .<br />

The f<strong>in</strong>al goal for the <strong>in</strong>dustrial partner [2] of this project is the<br />

production of a family of low-cost, low voltage, ultra-low power<br />

s<strong>in</strong>gle-die digital television receivers <strong>in</strong> advanced CMOS<br />

technologies (90 nm and smaller geometries). The first<br />

member of this family is the AS-101, which targets the<br />

follow<strong>in</strong>g ETSI [3] standards:<br />

• DVB-T, Digital Video Broadcast<strong>in</strong>g for low-power<br />

terrestrial digital television receivers<br />

• DVB-H, for mobile ultra-low-power multimedia receivers.<br />

The low power consumption, of less than 325 mW for DVB-T<br />

reception, together with the small footpr<strong>in</strong>t, less than 100 mm2 for a complete module, a very short bill of material, and a<br />

choice of standard host <strong>in</strong>terfaces (USB2.0, SDIO, SPI) make<br />

them ideal for a very wide range of mobile consumer<br />

applications.<br />

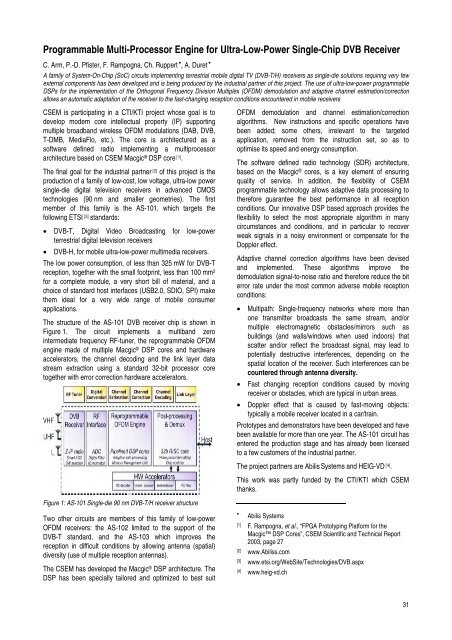

The structure of the AS-101 DVB receiver chip is shown <strong>in</strong><br />

Figure 1. The circuit implements a multiband zero<br />

<strong>in</strong>termediate frequency RF-tuner, the reprogrammable OFDM<br />

eng<strong>in</strong>e made of multiple Macgic ® DSP cores and hardware<br />

accelerators, the channel decod<strong>in</strong>g and the l<strong>in</strong>k layer data<br />

stream extraction us<strong>in</strong>g a standard 32-bit processor core<br />

together with error correction hardware accelerators.<br />

Figure 1: AS-101 S<strong>in</strong>gle-die 90 nm DVB-T/H receiver structure<br />

Two other circuits are members of this family of low-power<br />

OFDM receivers: the AS-102 limited to the support of the<br />

DVB-T standard, and the AS-103 which improves the<br />

reception <strong>in</strong> difficult conditions by allow<strong>in</strong>g antenna (spatial)<br />

diversity (use of multiple reception antennas).<br />

The <strong>CSEM</strong> has developed the Macgic ® DSP architecture. The<br />

DSP has been specially tailored and optimized to best suit<br />

OFDM demodulation and channel estimation/correction<br />

algorithms. New <strong>in</strong>structions and specific operations have<br />

been added; some others, irrelevant to the targeted<br />

application, removed from the <strong>in</strong>struction set, so as to<br />

optimise its speed and energy consumption.<br />

The software def<strong>in</strong>ed radio technology (SDR) architecture,<br />

based on the Macgic ® cores, is a key element of ensur<strong>in</strong>g<br />

quality of service. In addition, the flexibility of <strong>CSEM</strong><br />

programmable technology allows adaptive data process<strong>in</strong>g to<br />

therefore guarantee the best performance <strong>in</strong> all reception<br />

conditions. Our <strong>in</strong>novative DSP based approach provides the<br />

flexibility to select the most appropriate algorithm <strong>in</strong> many<br />

circumstances and conditions, and <strong>in</strong> particular to recover<br />

weak signals <strong>in</strong> a noisy environment or compensate for the<br />

Doppler effect.<br />

Adaptive channel correction algorithms have been devised<br />

and implemented. These algorithms improve the<br />

demodulation signal-to-noise ratio and therefore reduce the bit<br />

error rate under the most common adverse mobile reception<br />

conditions:<br />

• Multipath: S<strong>in</strong>gle-frequency networks where more than<br />

one transmitter broadcasts the same stream, and/or<br />

multiple electromagnetic obstacles/mirrors such as<br />

build<strong>in</strong>gs (and walls/w<strong>in</strong>dows when used <strong>in</strong>doors) that<br />

scatter and/or reflect the broadcast signal, may lead to<br />

potentially destructive <strong>in</strong>terferences, depend<strong>in</strong>g on the<br />

spatial location of the receiver. Such <strong>in</strong>terferences can be<br />

countered through antenna diversity.<br />

• Fast chang<strong>in</strong>g reception conditions caused by mov<strong>in</strong>g<br />

receiver or obstacles, which are typical <strong>in</strong> urban areas.<br />

• Doppler effect that is caused by fast-mov<strong>in</strong>g objects:<br />

typically a mobile receiver located <strong>in</strong> a car/tra<strong>in</strong>.<br />

Prototypes and demonstrators have been developed and have<br />

been available for more than one year. The AS-101 circuit has<br />

entered the production stage and has already been licensed<br />

to a few customers of the <strong>in</strong>dustrial partner.<br />

The project partners are Abilis Systems and HEIG-VD [4] .<br />

This work was partly funded by the CTI/KTI which <strong>CSEM</strong><br />

thanks.<br />

•<br />

Abilis Systems<br />

[1] F. Rampogna, et al., “FPGA Prototyp<strong>in</strong>g Platform for the<br />

Macgic DSP Cores”, <strong>CSEM</strong> Scientific and Technical Report<br />

2003, page 27<br />

[2] www.Abiliss.com<br />

[3] www.etsi.org/WebSite/Technologies/DVB.aspx<br />

[4] www.heig-vd.ch<br />

31