Logic selection guide 2016

1Sk34oD

1Sk34oD

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

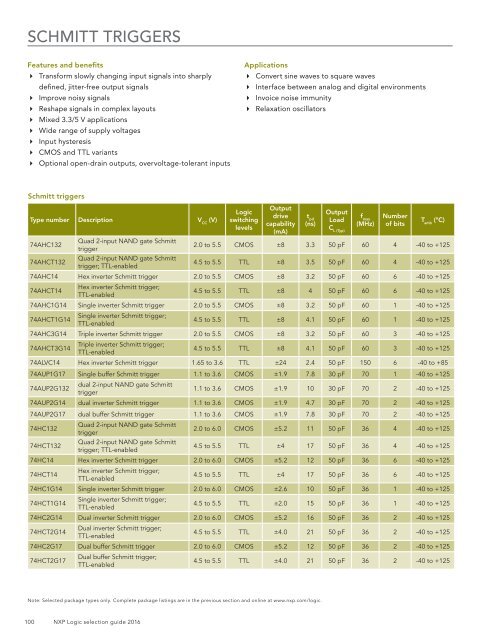

SCHMITT TRIGGERS<br />

Features and benefits<br />

4 Transform slowly changing input signals into sharply<br />

defined, jitter-free output signals<br />

4 Improve noisy signals<br />

4 Reshape signals in complex layouts<br />

4 Mixed 3.3/5 V applications<br />

4 Wide range of supply voltages<br />

4 Input hysteresis<br />

4 CMOS and TTL variants<br />

4 Optional open-drain outputs, overvoltage-tolerant inputs<br />

Applications<br />

4 Convert sine waves to square waves<br />

4 Interface between analog and digital environments<br />

4 Invoice noise immunity<br />

4 Relaxation oscillators<br />

Schmitt triggers (cont.)<br />

Type number Description V CC<br />

(V)<br />

74AHC132<br />

74AHCT132<br />

Quad 2-input NAND gate Schmitt<br />

trigger<br />

Quad 2-input NAND gate Schmitt<br />

trigger; TTL-enabled<br />

<strong>Logic</strong><br />

switching<br />

levels<br />

Output<br />

drive<br />

capability<br />

(mA)<br />

t pd<br />

(ns)<br />

Output<br />

Load<br />

C L (Typ)<br />

f max<br />

(MHz)<br />

Number<br />

of bits<br />

T amb<br />

(°C)<br />

2.0 to 5.5 CMOS ±8 3.3 50 pF 60 4 -40 to +125<br />

4.5 to 5.5 TTL ±8 3.5 50 pF 60 4 -40 to +125<br />

74AHC14 Hex inverter Schmitt trigger 2.0 to 5.5 CMOS ±8 3.2 50 pF 60 6 -40 to +125<br />

74AHCT14<br />

Hex inverter Schmitt trigger;<br />

TTL-enabled<br />

4.5 to 5.5 TTL ±8 4 50 pF 60 6 -40 to +125<br />

74AHC1G14 Single inverter Schmitt trigger 2.0 to 5.5 CMOS ±8 3.2 50 pF 60 1 -40 to +125<br />

74AHCT1G14<br />

Single inverter Schmitt trigger;<br />

TTL-enabled<br />

4.5 to 5.5 TTL ±8 4.1 50 pF 60 1 -40 to +125<br />

74AHC3G14 Triple inverter Schmitt trigger 2.0 to 5.5 CMOS ±8 3.2 50 pF 60 3 -40 to +125<br />

74AHCT3G14<br />

Triple inverter Schmitt trigger;<br />

TTL-enabled<br />

4.5 to 5.5 TTL ±8 4.1 50 pF 60 3 -40 to +125<br />

74ALVC14 Hex inverter Schmitt trigger 1.65 to 3.6 TTL ±24 2.4 50 pF 150 6 -40 to +85<br />

74AUP1G17 Single buffer Schmitt trigger 1.1 to 3.6 CMOS ±1.9 7.8 30 pF 70 1 -40 to +125<br />

74AUP2G132<br />

dual 2-input NAND gate Schmitt<br />

trigger<br />

1.1 to 3.6 CMOS ±1.9 10 30 pF 70 2 -40 to +125<br />

74AUP2G14 dual inverter Schmitt trigger 1.1 to 3.6 CMOS ±1.9 4.7 30 pF 70 2 -40 to +125<br />

74AUP2G17 dual buffer Schmitt trigger 1.1 to 3.6 CMOS ±1.9 7.8 30 pF 70 2 -40 to +125<br />

74HC132<br />

74HCT132<br />

Quad 2-input NAND gate Schmitt<br />

trigger<br />

Quad 2-input NAND gate Schmitt<br />

trigger; TTL-enabled<br />

2.0 to 6.0 CMOS ±5.2 11 50 pF 36 4 -40 to +125<br />

4.5 to 5.5 TTL ±4 17 50 pF 36 4 -40 to +125<br />

74HC14 Hex inverter Schmitt trigger 2.0 to 6.0 CMOS ±5.2 12 50 pF 36 6 -40 to +125<br />

74HCT14<br />

Hex inverter Schmitt trigger;<br />

TTL-enabled<br />

4.5 to 5.5 TTL ±4 17 50 pF 36 6 -40 to +125<br />

74HC1G14 Single inverter Schmitt trigger 2.0 to 6.0 CMOS ±2.6 10 50 pF 36 1 -40 to +125<br />

74HCT1G14<br />

Single inverter Schmitt trigger;<br />

TTL-enabled<br />

4.5 to 5.5 TTL ±2.0 15 50 pF 36 1 -40 to +125<br />

74HC2G14 Dual inverter Schmitt trigger 2.0 to 6.0 CMOS ±5.2 16 50 pF 36 2 -40 to +125<br />

74HCT2G14<br />

Dual inverter Schmitt trigger;<br />

TTL-enabled<br />

4.5 to 5.5 TTL ±4.0 21 50 pF 36 2 -40 to +125<br />

74HC2G17 Dual buffer Schmitt trigger 2.0 to 6.0 CMOS ±5.2 12 50 pF 36 2 -40 to +125<br />

74HCT2G17<br />

Dual buffer Schmitt trigger;<br />

TTL-enabled<br />

4.5 to 5.5 TTL ±4.0 21 50 pF 36 2 -40 to +125<br />

Note: Selected package types only. Complete package listings are in the previous section and online at www.nxp.com/logic.<br />

100 NXP <strong>Logic</strong> <strong>selection</strong> <strong>guide</strong> <strong>2016</strong>