Logic selection guide 2016

1Sk34oD

1Sk34oD

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

OVERVOLTAGE-TOLERANT OUTPUTS<br />

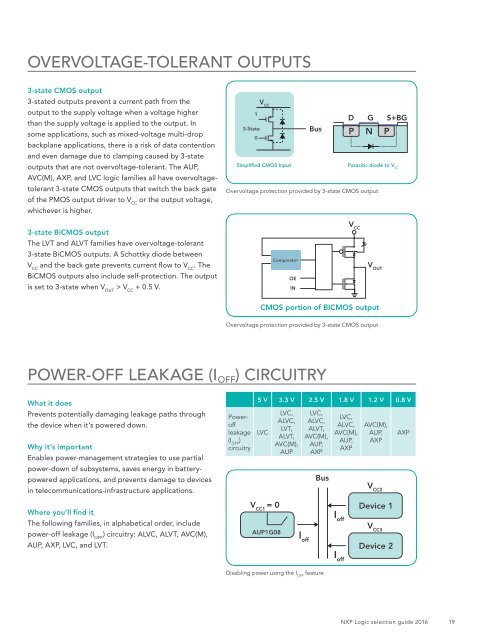

3-state CMOS output<br />

3-stated outputs prevent a current path from the<br />

output to the supply voltage when a voltage higher<br />

than the supply voltage is applied to the output. In<br />

some applications, such as mixed-voltage multi-drop<br />

backplane applications, there is a risk of data contention<br />

and even damage due to clamping caused by 3-state<br />

outputs that are not overvoltage-tolerant. The AUP,<br />

AVC(M), AXP, and LVC logic families all have overvoltagetolerant<br />

3-state CMOS outputs that switch the back gate<br />

of the PMOS output driver to V CC<br />

or the output voltage,<br />

whichever is higher.<br />

V CC<br />

1<br />

3-State<br />

0<br />

Simplified CMOS Input<br />

Bus<br />

D G S+BG<br />

P N P<br />

Parasitic diode to V CC<br />

Overvoltage protection provided by 3-state CMOS output<br />

3-state BiCMOS output<br />

V CC<br />

The LVT and ALVT families have overvoltage-tolerant<br />

3-state BiCMOS outputs. A Schottky diode between<br />

V CC<br />

and the back gate prevents current flow to V CC<br />

. The<br />

Comparator<br />

V OUT<br />

BiCMOS outputs also include self-protection. The output<br />

is set to 3-state when V OUT<br />

> V CC<br />

+ 0.5 V.<br />

OE<br />

IN<br />

CMOS portion of BICMOS output<br />

Overvoltage protection provided by 3-state CMOS output<br />

POWER-OFF LEAKAGE (I OFF ) CIRCUITRY<br />

What it does<br />

Prevents potentially damaging leakage paths through<br />

the device when it’s powered down.<br />

Why it’s important<br />

Enables power-management strategies to use partial<br />

power-down of subsystems, saves energy in batterypowered<br />

applications, and prevents damage to devices<br />

in telecommunications-infrastructure applications.<br />

Poweroff<br />

leakage<br />

(I OFF<br />

)<br />

circuitry<br />

5 V 3.3 V 2.5 V 1.8 V 1.2 V 0.8 V<br />

LVC<br />

LVC,<br />

ALVC,<br />

LVT,<br />

ALVT,<br />

AVC(M),<br />

AUP<br />

LVC,<br />

ALVC,<br />

ALVT,<br />

AVC(M),<br />

AUP,<br />

AXP<br />

Bus<br />

LVC,<br />

ALVC,<br />

AVC(M),<br />

AUP,<br />

AXP<br />

AVC(M),<br />

AUP,<br />

AXP<br />

V CC2<br />

AXP<br />

Where you’ll find it<br />

The following families, in alphabetical order, include<br />

power-off leakage (I OFF<br />

) circuitry: ALVC, ALVT, AVC(M),<br />

AUP, AXP, LVC, and LVT.<br />

V CC1<br />

= 0<br />

AUP1G08<br />

I off<br />

Device 1<br />

I off<br />

V CC3<br />

I off<br />

Device 2<br />

Disabling power using the I OFF<br />

feature<br />

NXP <strong>Logic</strong> <strong>selection</strong> <strong>guide</strong> <strong>2016</strong><br />

19