Logic selection guide 2016

1Sk34oD

1Sk34oD

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

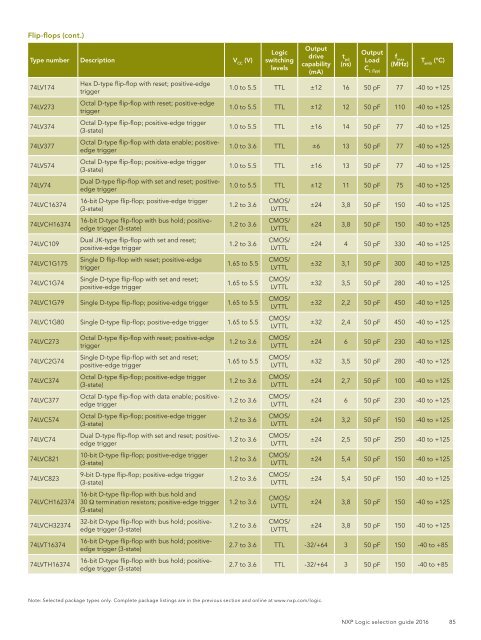

Flip-flops (cont.)<br />

Type number Description V CC<br />

(V)<br />

74LV174<br />

74LV273<br />

74LV374<br />

74LV377<br />

74LV574<br />

74LV74<br />

74LVC16374<br />

74LVCH16374<br />

74LVC109<br />

74LVC1G175<br />

74LVC1G74<br />

Hex D-type flip-flop with reset; positive-edge<br />

trigger<br />

Octal D-type flip-flop with reset; positive-edge<br />

trigger<br />

Octal D-type flip-flop; positive-edge trigger<br />

(3-state)<br />

Octal D-type flip-flop with data enable; positiveedge<br />

trigger<br />

Octal D-type flip-flop; positive-edge trigger<br />

(3-state)<br />

Dual D-type flip-flop with set and reset; positiveedge<br />

trigger<br />

16-bit D-type flip-flop; positive-edge trigger<br />

(3-state)<br />

16-bit D-type flip-flop with bus hold; positiveedge<br />

trigger (3-state)<br />

Dual JK-type flip-flop with set and reset;<br />

positive-edge trigger<br />

Single D flip-flop with reset; positive-edge<br />

trigger<br />

Single D-type flip-flop with set and reset;<br />

positive-edge trigger<br />

<strong>Logic</strong><br />

switching<br />

levels<br />

Output<br />

drive<br />

capability<br />

(mA)<br />

t pd<br />

(ns)<br />

Output<br />

Load<br />

C L (Typ)<br />

f max<br />

(MHz)<br />

T amb<br />

(°C)<br />

1.0 to 5.5 TTL ±12 16 50 pF 77 -40 to +125<br />

1.0 to 5.5 TTL ±12 12 50 pF 110 -40 to +125<br />

1.0 to 5.5 TTL ±16 14 50 pF 77 -40 to +125<br />

1.0 to 3.6 TTL ±6 13 50 pF 77 -40 to +125<br />

1.0 to 5.5 TTL ±16 13 50 pF 77 -40 to +125<br />

1.0 to 5.5 TTL ±12 11 50 pF 75 -40 to +125<br />

1.2 to 3.6<br />

1.2 to 3.6<br />

1.2 to 3.6<br />

1.65 to 5.5<br />

1.65 to 5.5<br />

74LVC1G79 Single D-type flip-flop; positive-edge trigger 1.65 to 5.5<br />

74LVC1G80 Single D-type flip-flop; positive-edge trigger 1.65 to 5.5<br />

74LVC273<br />

74LVC2G74<br />

74LVC374<br />

74LVC377<br />

74LVC574<br />

74LVC74<br />

74LVC821<br />

74LVC823<br />

74LVCH162374<br />

74LVCH32374<br />

74LVT16374<br />

74LVTH16374<br />

Octal D-type flip-flop with reset; positive-edge<br />

trigger<br />

Single D-type flip-flop with set and reset;<br />

positive-edge trigger<br />

Octal D-type flip-flop; positive-edge trigger<br />

(3-state)<br />

Octal D-type flip-flop with data enable; positiveedge<br />

trigger<br />

Octal D-type flip-flop; positive-edge trigger<br />

(3-state)<br />

Dual D-type flip-flop with set and reset; positiveedge<br />

trigger<br />

10-bit D-type flip-flop; positive-edge trigger<br />

(3-state)<br />

9-bit D-type flip-flop; positive-edge trigger<br />

(3-state)<br />

16-bit D-type flip-flop with bus hold and<br />

30 Ω termination resistors; positive-edge trigger<br />

(3-state)<br />

32-bit D-type flip-flop with bus hold; positiveedge<br />

trigger (3-state)<br />

16-bit D-type flip-flop with bus hold; positiveedge<br />

trigger (3-state)<br />

16-bit D-type flip-flop with bus hold; positiveedge<br />

trigger (3-state)<br />

1.2 to 3.6<br />

1.65 to 5.5<br />

1.2 to 3.6<br />

1.2 to 3.6<br />

1.2 to 3.6<br />

1.2 to 3.6<br />

1.2 to 3.6<br />

1.2 to 3.6<br />

1.2 to 3.6<br />

1.2 to 3.6<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

CMOS/<br />

LVTTL<br />

±24 3,8 50 pF 150 -40 to +125<br />

±24 3,8 50 pF 150 -40 to +125<br />

±24 4 50 pF 330 -40 to +125<br />

±32 3,1 50 pF 300 -40 to +125<br />

±32 3,5 50 pF 280 -40 to +125<br />

±32 2,2 50 pF 450 -40 to +125<br />

±32 2,4 50 pF 450 -40 to +125<br />

±24 6 50 pF 230 -40 to +125<br />

±32 3,5 50 pF 280 -40 to +125<br />

±24 2,7 50 pF 100 -40 to +125<br />

±24 6 50 pF 230 -40 to +125<br />

±24 3,2 50 pF 150 -40 to +125<br />

±24 2,5 50 pF 250 -40 to +125<br />

±24 5,4 50 pF 150 -40 to +125<br />

±24 5,4 50 pF 150 -40 to +125<br />

±24 3,8 50 pF 150 -40 to +125<br />

±24 3,8 50 pF 150 -40 to +125<br />

2.7 to 3.6 TTL -32/+64 3 50 pF 150 -40 to +85<br />

2.7 to 3.6 TTL -32/+64 3 50 pF 150 -40 to +85<br />

Note: Selected package types only. Complete package listings are in the previous section and online at www.nxp.com/logic.<br />

NXP <strong>Logic</strong> <strong>selection</strong> <strong>guide</strong> <strong>2016</strong><br />

85