Logic selection guide 2016

1Sk34oD

1Sk34oD

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

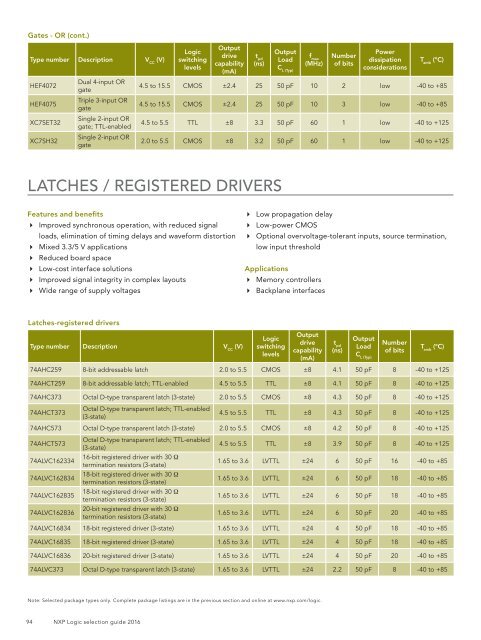

Gates - OR (cont.)<br />

Type number Description V CC<br />

(V)<br />

HEF4072<br />

HEF4075<br />

XC7SET32<br />

XC7SH32<br />

Dual 4-input OR<br />

gate<br />

Triple 3-input OR<br />

gate<br />

Single 2-input OR<br />

gate; TTL-enabled<br />

Single 2-input OR<br />

gate<br />

<strong>Logic</strong><br />

switching<br />

levels<br />

Output<br />

drive<br />

capability<br />

(mA)<br />

t pd<br />

(ns)<br />

Output<br />

Load<br />

C L (Typ)<br />

f max<br />

(MHz)<br />

Number<br />

of bits<br />

Power<br />

dissipation<br />

considerations<br />

T amb<br />

(°C)<br />

4.5 to 15.5 CMOS ±2.4 25 50 pF 10 2 low -40 to +85<br />

4.5 to 15.5 CMOS ±2.4 25 50 pF 10 3 low -40 to +85<br />

4.5 to 5.5 TTL ±8 3.3 50 pF 60 1 low -40 to +125<br />

2.0 to 5.5 CMOS ±8 3.2 50 pF 60 1 low -40 to +125<br />

LATCHES / REGISTERED DRIVERS<br />

Features and benefits<br />

4 Improved synchronous operation, with reduced signal<br />

loads, elimination of timing delays and waveform distortion<br />

4 Mixed 3.3/5 V applications<br />

4 Reduced board space<br />

4 Low-cost interface solutions<br />

4 Improved signal integrity in complex layouts<br />

4 Wide range of supply voltages<br />

4 Low propagation delay<br />

4 Low-power CMOS<br />

4 Optional overvoltage-tolerant inputs, source termination,<br />

low input threshold<br />

Applications<br />

4 Memory controllers<br />

4 Backplane interfaces<br />

Latches-registered drivers (cont.)<br />

Type number Description V CC<br />

(V)<br />

<strong>Logic</strong><br />

switching<br />

levels<br />

Output<br />

drive<br />

capability<br />

(mA)<br />

t pd<br />

(ns)<br />

Output<br />

Load<br />

C L (Typ)<br />

Number<br />

of bits<br />

T amb<br />

(°C)<br />

74AHC259 8-bit addressable latch 2.0 to 5.5 CMOS ±8 4.1 50 pF 8 -40 to +125<br />

74AHCT259 8-bit addressable latch; TTL-enabled 4.5 to 5.5 TTL ±8 4.1 50 pF 8 -40 to +125<br />

74AHC373 Octal D-type transparent latch (3-state) 2.0 to 5.5 CMOS ±8 4.3 50 pF 8 -40 to +125<br />

74AHCT373<br />

Octal D-type transparent latch; TTL-enabled<br />

(3-state)<br />

4.5 to 5.5 TTL ±8 4.3 50 pF 8 -40 to +125<br />

74AHC573 Octal D-type transparent latch (3-state) 2.0 to 5.5 CMOS ±8 4.2 50 pF 8 -40 to +125<br />

74AHCT573<br />

74ALVC162334<br />

74ALVC162834<br />

74ALVC162835<br />

74ALVC162836<br />

Octal D-type transparent latch; TTL-enabled<br />

(3-state)<br />

16-bit registered driver with 30 Ω<br />

termination resistors (3-state)<br />

18-bit registered driver with 30 Ω<br />

termination resistors (3-state)<br />

18-bit registered driver with 30 Ω<br />

termination resistors (3-state)<br />

20-bit registered driver with 30 Ω<br />

termination resistors (3-state)<br />

4.5 to 5.5 TTL ±8 3.9 50 pF 8 -40 to +125<br />

1.65 to 3.6 LVTTL ±24 6 50 pF 16 -40 to +85<br />

1.65 to 3.6 LVTTL ±24 6 50 pF 18 -40 to +85<br />

1.65 to 3.6 LVTTL ±24 6 50 pF 18 -40 to +85<br />

1.65 to 3.6 LVTTL ±24 6 50 pF 20 -40 to +85<br />

74ALVC16834 18-bit registered driver (3-state) 1.65 to 3.6 LVTTL ±24 4 50 pF 18 -40 to +85<br />

74ALVC16835 18-bit registered driver (3-state) 1.65 to 3.6 LVTTL ±24 4 50 pF 18 -40 to +85<br />

74ALVC16836 20-bit registered driver (3-state) 1.65 to 3.6 LVTTL ±24 4 50 pF 20 -40 to +85<br />

74ALVC373 Octal D-type transparent latch (3-state) 1.65 to 3.6 LVTTL ±24 2.2 50 pF 8 -40 to +85<br />

Note: Selected package types only. Complete package listings are in the previous section and online at www.nxp.com/logic.<br />

94 NXP <strong>Logic</strong> <strong>selection</strong> <strong>guide</strong> <strong>2016</strong>